S29GL01GP12TFI020 Spansion Inc., S29GL01GP12TFI020 Datasheet

S29GL01GP12TFI020

Specifications of S29GL01GP12TFI020

Available stocks

Related parts for S29GL01GP12TFI020

S29GL01GP12TFI020 Summary of contents

Page 1

S29GL-P MirrorBit S29GL01GP, S29GL512P, S29GL256P, S29GL128P 1 Gigabit, 512 Megabit, 256 Megabit and 128 Megabit 3.0 Volt-only Page Mode Flash Memory featuring 90 nm MirrorBit Process Technology Data Sheet (Preliminary) Notice to Readers: This document states the current technical specifications ...

Page 2

... Spansion Inc. The information is intended to help you evaluate this product. Do not design in this product without contacting the factory. Spansion Inc. reserves the right to change or discontinue work on this proposed product without notice.” ...

Page 3

S29GL-P MirrorBit S29GL01GP, S29GL512P, S29GL256P, S29GL128P 1 Gigabit, 512 Megabit, 256 Megabit and 128 Megabit 3.0 Volt-only Page Mode Flash Memory featuring 90 nm MirrorBit Process Technology Data Sheet (Preliminary) General Description The Spansion S29GL01G/512/256/128P are Mirrorbit offer a fast ...

Page 4

Performance Characteristics Density Voltage Range Regulated V 128 & 256 Mb VersatileIO V Regulated V 512 Mb VersatileIO V Regulated VersatileIO V Notes 1. Access times are dependent on V See Ordering Information Regulated ...

Page 5

Table of Contents General Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . ...

Page 6

Appendix . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . ...

Page 7

Figures Figure 3.1 S29GL-P Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . ...

Page 8

Tables Table 2.1 Input/Output Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . ...

Page 9

Ordering Information The ordering part number is formed by a valid combination of the following: S29GL01GP DEVICE NUMBER/DESCRIPTION S29GL01GP, S29GL512P, S29GL256P, S29GL128P 3.0 Volt-only, 1024, 512, 256 and 128 Megabit ...

Page 10

Recommended Combinations Recommended Combinations list configurations planned to be supported in volume for this device. Consult your local sales office to confirm availability of specific recommended combinations and to check on newly released combinations. Base Part Number S29GL01GP 10 (1), ...

Page 11

Input/Output Descriptions & Logic Symbol Table 2.1 identifies the input and output package connections provided on the device. Symbol Type A25–A0 Input DQ14–DQ0 I/O DQ15/A-1 I/O CE# Input OE# Input WE# Input V Supply CC ...

Page 12

Block Diagram RY/BY RESET# WE# State WP#/ACC Control BYTE# Command Register CE# OE# V Detector CC A **–A0 (A-1) Max ** A GL01GP=A25, A GL512P = A24, A Max Max Max 4. Physical ...

Page 13

RFU A7 A13 WE# RESET# A4 RY/BY# WP#/ACC RFU Note RFU = No Connect (NC) November 28, 2007 S29GL-P_00_A8 ...

Page 14

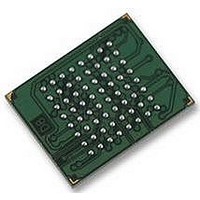

LAA064—64 ball Fortified Ball Grid Array Figure 4.2 LAA064—64ball Fortified Ball Grid Array (FBGA ...

Page 15

A23 1 A22 2 A15 3 A14 4 A13 5 A12 6 A11 7 A10 A19 11 A20 12 WE# 13 RESET# 14 A21 15 WP#/ACC 16 RY/BY# 17 A18 18 ...

Page 16

TS056—56-Pin Standard Thin Small Outline Package (TSOP) Figure 4.4 56-Pin Thin Small Outline Package (TSOP PACKAGE TS 56 JEDEC MO-142 (B) EC SYMBOL MIN. NOM. MAX. A --- --- 1.20 A1 0.05 --- 0.15 A2 ...

Page 17

Additional Resources Visit www.spansion.com 5.1 Application Notes The following is a list of application notes related to this product. All Spansion application notes are available at http://www.spansion.com/support/technical_documents/application_notes.html Using the Operation Status Bits in AMD Devices ...

Page 18

Product Overview The S29GL-P family consists of 1 Gb, 512 Mb, 256 Mb and 128 Mb, 3.0-volt-only, page mode Flash devices optimized for today’s embedded designs that demand a large storage array and rich functionality. These devices are manufactured ...

Page 19

Uniform Sector Size 64 Kword/128 Kb Note This table has been condensed to show sector-related information for an entire device on a single page. Sectors and their address ranges that are not explicitly listed (such as ...

Page 20

Word/Byte Configuration The BYTE# pin controls whether the device data I/O pins operate in the byte or word configuration. If the BYTE# pin is set at logic ‘1’, the device is in word configuration, DQ0-DQ15 are active and controlled ...

Page 21

7.6 Autoselect The Autoselect mode provides manufacturer ID, Device identification, and sector protection information, through identifier codes output from the internal register (separate from the memory array) on DQ7-DQ0. This mode is primarily intended for programming ...

Page 22

Table 7.2 Autoselect Codes, (High Voltage Method) Description CE# OE# WE# Manufacturer ID Spansion Product Cycle 1 Cycle Cycle 3 Cycle 1 Cycle Cycle 3 Cycle 1 Cycle 2 ...

Page 23

Cycle Unlock Cycle 1 Unlock Cycle 2 Autoselect Command Software Functions and Sample Code Cycle Unlock Cycle 1 Note 1. Any offset within the device works. 2. base = base address. The following ...

Page 24

Program/Erase Operations These devices are capable of several modes of programming and or erase operations which are described in detail in the following sections. During a write operation, the system must drive CE# and WE command, and ...

Page 25

PASS. Device is in November 28, 2007 S29GL-P_00_A8 Figure 7.1 Single Word Program Write Unlock Cycles: Address 555h, ...

Page 26

Software Functions and Sample Code Cycle Unlock Cycle 1 Unlock Cycle 2 Program Setup Program Note Base = Base Address. The following source code example of using the single word program function. Refer to the Spansion Low ...

Page 27

The write-buffer “embedded” programming operation can be suspended using the standard suspend/resume commands. Upon successful completion of the Write Buffer Programming operation, the device returns to READ mode. The Write Buffer Programming Sequence is ABORTED under ...

Page 28

Software Functions and Sample Code (LLD Functions Used = lld_WriteToBufferCmd, lld_ProgramBufferToFlashCmd) Cycle Description Write Buffer Load Command 4 Write Word Count Number of words (N) loaded into the write buffer can be from words ...

Page 29

Write Next Word, Decrement wc – 1 RESET. Issue Write Buffer Abort Reset Command November 28, 2007 S29GL-P_00_A8 ...

Page 30

Sector Erase The sector erase function erases one or more sectors in the memory array. (See Figure 7.3.) The device does not require the system to preprogram a sector prior to erase. The Embedded Erase algorithm automatically programs and ...

Page 31

Write Unlock Cycles: Address 555h, Data AAh Address 2AAh, Data 55h Write Sector Erase Cycles: Address 555h, Data 80h Address 555h, Data AAh Address 2AAh, Data 55h Sector Address, Data 30h Select No Additional Sectors? Yes ...

Page 32

Chip Erase Command Sequence Chip erase is a six-bus cycle operation as indicated by Embedded Erase algorithm, which does not require the system to preprogram prior to erase. The Embedded Erase algorithm automatically preprograms and verifies the entire memory ...

Page 33

7.7.5 Erase Suspend/Erase Resume Commands The Erase Suspend command allows the system to interrupt a sector erase operation and then read data from, or program data to, any sector not selected for erasure. The sector address ...

Page 34

Program Suspend/Program Resume Commands The Program Suspend command allows the system to interrupt an embedded programming operation or a “Write to Buffer” programming operation so that data can read from any non-suspended sector. When the Program Suspend command is ...

Page 35

7.7.7 Accelerated Program Accelerated single word programming and write buffer programming operations are enabled through the WP#/ACC pin. This method is faster than the standard program command sequences. Note The accelerated program functions must not be ...

Page 36

Cycle 1 Program Setup Command 2 Program Command /* Example: Unlock Bypass Program Command /* Do while in Unlock Bypass Entry Mode! *( (UINT16 *)base_addr ) = 0x00A0; *( (UINT16 *) Poll until done or error ...

Page 37

the status or valid data. Even if the device has completed the program or erase operation and DQ7 has valid data, the data outputs on DQ6-DQ0 may be still invalid. Valid data on DQ7-D00 appears on ...

Page 38

DQ6: Toggle Bit I Toggle Bit I on DQ6 indicates whether an Embedded Program or Erase algorithm is in progress or complete, or whether the device has entered the Erase Suspend mode. Toggle Bit I may be read at ...

Page 39

this toggling behavior to be properly observed, the consecutive status bit reads must not be interleaved with read accesses to other memory sectors not possible to temporarily prevent reads to other memory sectors, ...

Page 40

Status Embedded Program Algorithm Standard Mode Embedded Erase Algorithm Program Program- Suspend Suspend Mode Read Erase- Suspend Erase Read Suspend Mode Erase-Suspend-Program (Embedded Program) Write-to- Buffer Notes 1. DQ5 switches to 1 when an Embedded Program, Embedded Erase, or Write-to-Buffer ...

Page 41

7.9.3 Software Reset Software reset is part of the command set (see read mode and must be used for the following conditions exit Autoselect mode 2. when DQ5 goes high during write status operation ...

Page 42

Advanced Sector Protection/Unprotection The Advanced Sector Protection/Unprotection feature disables or enables programming or erase operations in any or all sectors and can be implemented through software and/or hardware methods, which are independent of each other. This section describes the ...

Page 43

8.1 Lock Register As shipped from the factory, all devices default to the persistent mode when power is applied, and all sectors are unprotected, unless otherwise chosen through the DYB ordering option (see on page 9). ...

Page 44

There are no means for individually erasing a specific PPB and no specific sector address is required for this operation. 9. Exit command must be issued after the execution which resets the device to read mode and re- enables ...

Page 45

8.2.1 Dynamic Protection Bits Dynamic Protection Bits are volatile and unique for each sector and can be individually modified. DYBs only control the protection scheme for unprotected sectors that have their PPBs cleared (erased to “1”). ...

Page 46

There is no means to verify what the password is after it is set. 6. The Password Mode Lock Bit, once set, prevents reading the 64-bit password on the data bus and further password programming. 7. The Password Mode ...

Page 47

Write Unlock Cycles: Address 555h, Data AAh Address 2AAh, Data 55h Enter Lock Register Command: Address 555h, Data 40h Program Lock Register Data Address XXXh, Data A0h Address XXXh*, Data PD Perform Polling Algorithm (see Write ...

Page 48

Advanced Sector Protection Software Examples Table 8.2 Sector Protection Schemes: DYB, PPB and PPB Lock Bit Combinations Unique Device PPB Lock Bit 0 = locked 1 = unlocked Any Sector Any Sector Any Sector Any Sector Any Sector Any ...

Page 49

8.6.3 Write Pulse “Glitch Protection” Noise pulses of less than 5 ns (typical) on OE#, CE# or WE# do not initiate a write cycle. 8.6.4 Power-Up Write Inhibit If WE# = CE# = RESET ...

Page 50

Secured Silicon Sector Flash Memory Region The Secured Silicon Sector provides an extra Flash memory region that enables permanent part identification through an Electronic Serial Number (ESN). The Secured Silicon Sector is 128 words in length and all Secured ...

Page 51

10.2 Customer Lockable Secured Silicon Sector The Customer Lockable Secured Silicon Sector is always shipped unprotected (DQ7 set to “0”), allowing customers to utilize that sector in any manner they choose. If the security feature is ...

Page 52

Cycle Unlock Cycle 1 Unlock Cycle 2 Program Setup Program Note Base = Base Address. /* Once in the SecSi Sector mode, you program */ /* words using the programming algorithm. Cycle Unlock Cycle 1 Unlock Cycle 2 Exit Cycle ...

Page 53

11. Electrical Specifications 11.1 Absolute Maximum Ratings Description Storage Temperature, Plastic Packages Ambient Temperature with Power Applied Voltage with Respect to Ground Output Short Circuit Current (Note 3) Notes 1. Minimum DC voltage on input or ...

Page 54

Operating Ranges Ambient Temperature (TA), Industrial (I) Device Ambient Temperature (TA), Commercial (C) Device Supply Voltages V Supply Voltages IO Notes 1. Operating ranges define those limits between which the functionality of the device is guaranteed. 2. See also ...

Page 55

11.5 Switching Waveforms V IO Input 0 0.0 V Note If V < the input measurement reference level is 0 11.6 DC Characteristics Table 11.2 S29GL-P DC Characteristics (CMOS ...

Page 56

AC Characteristics 11.7.1 S29GL-P Read-Only Operations Parameter Description JEDEC Std. (Notes Read Cycle Time AVAV Address to Output Delay AVQV ACC t t Chip Enable to Output Delay ELQV CE t Page Access Time ...

Page 57

Addresses CE# OE# WE# Outputs RESET# RY/BY Amax:A3 A2:A0 (See Note) Data Bus CE# OE# Note Figure 11.6 shows word mode. Addresses are A2:A-1 for byte mode. November 28, 2007 S29GL-P_00_A8 ...

Page 58

Hardware Reset (RESET#) Parameter JEDEC Std. RESET# Pin Low (During Embedded Algorithms Ready Read Mode or Write mode RESET# Pin Low (NOT During Embedded Algorithms) t Ready to Read Mode or Write mode t RESET# Pulse Width ...

Page 59

CE# RESET# 11.7.3 S29GL-P Erase and Program Operations Table 11.6 S29GL-P Erase and Program Operations Parameter JEDEC Std. Description t t Write Cycle Time (Note 1) AVAV WC ...

Page 60

Program Command Sequence (last two cycles Addresses 555h CE# OE# WE Data RY/BY VCS Notes program address program data Illustration shows device in word mode. Figure ...

Page 61

Figure 11.11 Chip/Sector Erase Operation Timings Erase Command Sequence (last two cycles Addresses 2AAh CE Data 55h RY/BY# t VCS V CC Notes ...

Page 62

Figure 11.13 Toggle Bit Timings (During Embedded Algorithms) Addresses CE# t OEH WE# OE Valid Data DQ2 and DQ6 RY/BY# Note A = Valid address; not required for DQ6. Illustration shows first two status cycle after command sequence, ...

Page 63

11.7.4 S29GL-P Alternate CE# Controlled Erase and Program Operations Table 11.7 S29GL-P Alternate CE# Controlled Erase and Program Operations Parameter Description JEDEC Std. (Notes Write Cycle Time (Note 1) AVAV Address ...

Page 64

Figure 11.15 Alternate CE# Controlled Write (Erase/Program) Operation Timings 555 for program 2AA for erase Addresses WE# OE# CE Data t RH RESET# RY/BY# Notes 1. Figure 11.15 indicates last two bus cycles of ...

Page 65

11.7.5 Erase And Programming Performance Table 11.8 Erase And Programming Performance Parameter Sector Erase Time S29GL128P S29GL256P Chip Erase Time S29GL512P S29GL01GP Total Write Buffer Time (Note 3) Total Accelerated Write Buffer Programming Time (Note 3) ...

Page 66

Appendix This section contains information relating to software control or interfacing with the Flash device. For additional information and assistance regarding software, see the Spansion web site at www.spansion.com. 12.1 Command Definitions Writing specific address and data commands or ...

Page 67

Table 12.1 S29GL-P Memory Array Command Definitions, x16 Command (Notes) Read (6) 1 Reset (7) 1 Manufacturer ID 4 Device ID (8) 4 Sector Protect Verify (10) 4 Secure Device Verify (11) 4 CFI Query (12) ...

Page 68

Table 12.2 S29GL-P Sector Protection Command Definitions, x16 Command (Notes) Command Set Entry 3 Program (6) 2 Read (6) 1 Command Set Exit ( Command Set Entry 3 Password Program (9) 2 Password Read (10) 4 Password Unlock ...

Page 69

Table 12.3 S29GL-P Memory Array Command Definitions, x8 Command (Notes) Read (6) 1 Reset (7) 1 Manufacturer ID 4 Device ID (8) 4 Sector Protect Verify (10) 4 Secure Device Verify (11) 4 CFI Query (12) ...

Page 70

Table 12.4 S29GL-P Sector Protection Command Definitions, x8 Command (Notes) Command Set Entry 3 Bits Program (6) 2 Read (6) 1 Command Set Exit ( Command Set Entry 3 Password Program (9) 2 Password Read (10) 8 Password ...

Page 71

12.2 Common Flash Memory Interface The Common Flash Interface (CFI) specification outlines device and host system software interrogation handshake, which allows specific vendor-specified software algorithms to be used for entire families of devices. Software support can ...

Page 72

Addresses (x16) Addresses (x8) 1Bh 36h 1Ch 38h 1Dh 3Ah 1Eh 3Ch 1Fh 3Eh 20h 40h 21h 42h 22h 44h 23h 46h 24h 48h 25h 4Ah 26h 4Ch Addresses (x16) Addresses (x8) 27h 4Eh 28h 50h 29h 52h 2Ah 54h ...

Page 73

Table 12.8 Primary Vendor-Specific Extended Query Addresses (x16) Addresses (x8) 40h 80h 41h 82h 42h 84h 43h 86h 44h 88h 45h 8Ah 46h 8Ch 47h 8Eh 48h 90h 49h 92h 4Ah 94h 4Bh 96h 4Ch 98h ...

Page 74

Advance Information on S29GL MirrorBit Hardware Reset (RESET#) and Power-up Sequence Parameter t RESET# Low to CE# Low RPH t RESET# Pulse Width RP t Time between RESET# (high) and CE# (low) RH Note CE#, OE# and ...

Page 75

14. Revision History Section Revision A0 (October 29, 2004) Initial Release. Revision A1 (October 20, 2005) Global Revised all sections of document. Revision A2 (October 19, 2006) Revised all sections of document. Reformatted document to new ...

Page 76

Section Revision A8 (November 28, 2007) Ordering Information New commercial operating temperature option Operating Ranges New operating temperature range ...

Page 77

... Spansion assumes no liability for any damages of any kind arising out of the use of the information in this document. Copyright © 2004–2007 Spansion Inc. All rights reserved. Spansion ™ SIM and combinations thereof, are trademarks of Spansion LLC in the US and other countries ...