AD9222-65EBZ Analog Devices Inc, AD9222-65EBZ Datasheet

AD9222-65EBZ

Specifications of AD9222-65EBZ

Related parts for AD9222-65EBZ

AD9222-65EBZ Summary of contents

Page 1

... The available digital test patterns include built-in deterministic and pseudorandom patterns, along with custom user- defined test patterns entered via the serial port interface (SPI). The AD9222 is available in an RoHS compliant, 64-lead LFCSP specified over the industrial temperature range of −40°C to +85°C. PRODUCT HIGHLIGHTS 1 ...

Page 2

... AD9222 TABLE OF CONTENTS Features .............................................................................................. 1 Applications ....................................................................................... 1 General Description ......................................................................... 1 Functional Block Diagram .............................................................. 1 Product Highlights ........................................................................... 1 Revision History ............................................................................... 2 Specifications ..................................................................................... 3 AC Specifications .......................................................................... 4 Digital Specifications ................................................................... 5 Switching Specifications .............................................................. 6 Timing Diagrams .............................................................................. 7 Absolute Maximum Ratings ............................................................ 9 Thermal Impedance ..................................................................... 9 ESD Caution .................................................................................. 9 Pin Configuration and Function Descriptions ........................... 10 Equivalent Circuits ......................................................................... 12 Typical Performance Characteristics ........................................... 14 Theory of Operation ...................................................................... 21 REVISION HISTORY 4/10— ...

Page 3

... AD9222 Max Unit Bits ±8 mV ±8 mV ± ±0 ±0.6 LSB ±1 LSB ppm/°C ppm/°C ppm/°C ± kΩ V p-p ...

Page 4

... Full −80 Full −76 Full −92 Full −92 −80 Full −92 Full −90 25°C 80.0 25°C 77.0 Rev Page AD9222-65 Typ Max Min Typ Max 70.4 70.3 70.3 68.5 70.0 70.0 69.8 69.0 69.5 70.0 69.5 70.0 66.8 69.4 69 ...

Page 5

... Offset binary Offset binary LVDS LVDS 150 250 150 1.10 1.30 1.10 Offset binary Offset binary Rev Page AD9222 AD9222-65 Max Min Typ Max CMOS/LVDS/LVPECL 250 1.2 20 1.5 3.6 1.2 3.6 0.3 0.3 30 0.5 3.6 1.2 3 ...

Page 6

... SAMPLE SAMPLE SAMPLE + 300 − 300 ±50 ±200 ±50 600 600 375 375 8 8 750 750 <1 < Rev Page AD9222-65 Max Min Typ 65 10 7.5 7.5 3.1 1.5 2.3 300 300 3.1 1.5 2 FCO /24) (t /24) SAMPLE SAMPLE /24) (t /24) ...

Page 7

... Figure 2. 12-Bit Data Serial Stream, MSB First (Default FRAME t DATA MSB – – – – – – – 9 Figure 3. 10-Bit Data Serial Stream, MSB First Rev Page MSB N – – – – – – – MSB – – – – – – – 8 AD9222 D10 N – – 8 ...

Page 8

... AD9222 N – 1 VIN ± CLK– CLK+ t CPD DCO– DCO+ t FCO FCO– FCO – FRAME t DATA LSB – – – – – – – 9 Figure 4. 12-Bit Data Serial Stream, LSB First Rev Page D10 LSB D0 N – – – – ...

Page 9

... PCB with solid ground plane (simulated). Exposed pad JA soldered to PCB. −40°C to +85°C ESD CAUTION 150°C 300°C −65°C to +150°C Rev Page AD9222 1 θ θ θ 17.7°C/W 15.5°C/W 8.7°C/W 0.6°C/W ...

Page 10

... D − − PIN 1 INDICATOR AVDD AVDD 4 EXPOSED PADDLE, PIN 0 5 (BOTTOM OF PACKAGE) 6 AVDD 7 AD9222 AVDD 8 TOP VIEW CLK– 9 (Not to Scale) CLK+ 10 AVDD 11 AVDD – Figure 5. 64-Lead LFCSP Pin Configuration, Top View Description Analog Ground (Exposed Paddle) 1.8 V Analog Supply Digital Output Driver Ground 1 ...

Page 11

... ADC D Analog Input True External Resistor to Set the Internal ADC Core Bias Current Reference Mode Selection Voltage Reference Input/Output Differential Reference (Negative) Differential Reference (Positive) ADC E Analog Input True ADC E Analog Input Complement ADC F Analog Input Complement ADC F Analog Input True Rev Page AD9222 ...

Page 12

... AD9222 EQUIVALENT CIRCUITS VIN ± x Figure 6. Equivalent Analog Input Circuit 10Ω CLK+ 10kΩ 10kΩ 10Ω CLK– Figure 7. Equivalent Clock Input Circuit 350Ω SDIO/ODM 30kΩ Figure 8. Equivalent SDIO/ODM Input Circuit 1.25V SCLK/DTP AND PDWN Rev Page DRVDD ...

Page 13

... AVDD 70kΩ 1kΩ CSB Figure 12. Equivalent CSB Input Circuit 1kΩ SENSE Figure 13. Equivalent SENSE Circuit VREF Figure 14. Equivalent VREF Circuit Rev Page AD9222 6kΩ ...

Page 14

... IN 0 AIN = –0.5dBFS SNR = 70.02dB ENOB = 11.45 BITS –20 SFDR = 86.3dBc –40 –60 – FREQUENCY (MHz) Figure 19. Single-Tone 32k FFT with MHz, AD9222- AIN = –0.5dBFS SNR = 69.25dB ENOB = 11.21 BITS –20 SFDR = 72.85dBc –40 –60 – FREQUENCY (MHz) = 120 MHz, AD9222-50 ...

Page 15

... Figure 25. SNR/SFDR vs Figure 26. SNR/SFDR vs. f Rev Page AD9222 AIN = –0.5dBFS SNR = 68.67dB ENOB = 10.79 BITS SFDR = 71.49dBc FREQUENCY (MHz) = 120 MHz, AD9222- p-p, SFDR 2V p-p, SNR ENCODE (MSPS 2.61 MHz, AD9222-50 SAMPLE IN 2V p-p, SFDR 2V p-p, SNR ENCODE (MSPS 20.1 MHz, AD9222-50 ...

Page 16

... INPUT AMPLITUDE (dBFS) = 10.3 MHz, AD9222-65 IN 100 p-p, SFDR 70 80dB 60 REFERENCE p-p, SNR –60 –50 –40 –30 –20 INPUT AMPLITUDE (dBFS MHz, AD9222- p-p, SFDR 60 80dB REFERENCE LINE p-p, SNR –60 –50 –40 –30 –20 INPUT AMPLITUDE (dBFS MHz, AD9222-65 IN – ...

Page 17

... MHz, AD9222-50 IN1 IN2 0 AIN1 AND AIN2 = –7dBFS SFDR = 79.5dB IMD2 = 80.0dBc IMD3 = 84.1dBc FREQUENCY (MHz MHz and MHz, AD9222-65 IN1 IN2 0 AIN1 AND AIN2 = –7dBFS SFDR = 75.2dB IMD2 = 79.3dBc IMD3 = 75.1dBc FREQUENCY (MHz MHz and MHz, AD9222-65 IN1 IN2 AD9222 ...

Page 18

... MHz, AD9222-50 Figure 44. SINAD/SFDR vs. Temperature, f Rev Page p-p, SFDR p-p, SINAD 65 60 –40 – TEMPERATURE (°C) = 2.3 MHz, AD9222- p-p, SFDR p-p, SINAD –40 – TEMPERATURE (°C) = 20.1 MHz, AD9222- p-p, SFDR p-p, SINAD 65 60 –40 – TEMPERATURE (°C) = 19.7 MHz, AD9222- ...

Page 19

... N – 3 Figure 50. Input-Referred Noise Histogram, AD9222-50 Rev Page AD9222 500 1000 1500 2000 2500 3000 3500 CODE Figure 48. DNL MHz, AD9222- FREQUENCY (MHz) Figure 49. CMRR vs. Frequency, AD9222-50 0.27 LSB rms N – – CODE 4000 40 ...

Page 20

... Figure 52. Noise Power Ratio (NPR), AD9222-50 0.3 LSB rms Rev Page –1 –3dB BANDWIDTH = 325MHz –2 –3 –4 –5 –6 –7 –8 –9 –10 – 100 150 200 250 300 350 FREQUENCY (MHz) Figure 53. Full-Power Bandwidth vs. Frequency, AD9222-50 400 450 5 00 ...

Page 21

... Wideband A/D information. In general, the precise values depend on the application. The analog inputs of the AD9222 are not internally dc-biased. Therefore, in ac-coupled applications, the user must provide this bias externally. Setting the device so that V recommended for optimum performance, but the device can function over a wider range with reasonable performance, as shown in Figure 55 and Figure 57 ...

Page 22

... SFDR (dBc) SNR (dB) 0.2 0.4 0.6 0.8 1.0 1.2 ANALOG INPUT COMMON-MODE VOLTAGE (V) Figure 57. SNR/SFDR vs. Common-Mode Voltage MHz, AD9222-50 IN SFDR (dBc) SNR (dB) 0 0.2 0.4 0.6 0.8 1.0 1.2 ANALOG INPUT COMMON-MODE VOLTAGE (V) Figure 58. SNR/SFDR vs. Common-Mode Voltage MHz, AD9222-65 IN 1.4 1.6 1 ...

Page 23

... In the case of the AD9222, the largest input span available p-p. Differential Input Configurations There are several ways to drive the AD9222 either actively or passively; however, optimum performance is achieved by driving the analog input differentially. For example, using the ...

Page 24

... This signal is typically ac-coupled to the CLK+ and CLK− pins via a transformer or capacitors. These pins are biased internally and require no additional biasing. Figure 63 shows a preferred method for clocking the AD9222. The low jitter clock source is converted from a single-ended signal to a differential signal using an RF transformer. The back-to- back Schottky diodes across the secondary transformer limit clock excursions into the AD9222 to approximately 0 ...

Page 25

... ANALOG INPUT FREQUENCY (MHz) Figure 68. Ideal SNR vs. Input Frequency and Jitter Power Dissipation and Power-Down Mode As shown in Figure 69, the power dissipated by the AD9222 is proportional to its sample rate. The digital power dissipation does not vary much because it is determined primarily by the DRVDD supply and bias current of the LVDS output drivers. ...

Page 26

... AD9222 By asserting the PDWN pin high, the AD9222 is placed into power-down mode. In this state, the ADC typically dissipates 11 mW. During power-down, the LVDS output drivers are placed in a high impedance state. The AD9222 returns to normal operating mode when the PDWN pin is pulled low. This pin is both 1 ...

Page 27

... Less than 24 Inches on Standard FR-4, AD9222-65 500 EYE: ALL BITS ULS: 12067/12067 400 300 200 100 0 –100 –200 –300 –400 –500 –1.5ns –1.0ns –0.5ns 0ns 0.5ns 1.0ns 100 –200ps –100ps 0ps 100ps Greater than 24 Inches on Standard FR-4, AD9222-50 AD9222 1.5ns 150ps 1.5ns 200ps ...

Page 28

... Figure 78. Data Eye for LVDS Outputs in ANSI-644 Mode with 100 Ω Termination on and Trace Lengths Greater than 24 Inches on Standard FR-4, AD9222-65 The format of the output data is offset binary by default. An ULS: 12072/12072 example of the output coding format can be found in Table 8. ...

Page 29

... Two output clocks are provided to assist in capturing data from the AD9222. The DCO is used to clock the output data and is equal to six times the sample clock (CLK) rate. Data is clocked out of the AD9222 and must be captured on the rising and Table 9. Flexible Output Test Modes ...

Page 30

... ITU-T 0.150 (05/96) standard. The only differences are that the starting value must be a specific value instead of all 1s (see Table 10 for the initial values) and the AD9222 inverts the bit stream with relation to the ITU standard. Table 10. PN Sequence ...

Page 31

... Voltage Reference A stable, accurate 0.5 V voltage reference is built into the AD9222. This is gained up internally by a factor of 2, setting V to 1.0 V, which results in a full-scale differential input span REF p-p. The V is set internally by default ...

Page 32

... REFT and REFB, for the ADC core. Therefore, the external reference must be limited to a nominal of 1 –5 –10 –15 –20 –25 –30 0 0.5 1.0 1.5 2.0 CURRENT LOAD (mA) Figure 81. V Accuracy vs. Load, AD9222-50 REF 0.02 0 –0.02 –0.04 –0.06 –0.08 –0.10 –0.12 –0.14 –0.16 –0.18 –40 2.5 3.0 3.5 Rev Page – ...

Page 33

... SERIAL PORT INTERFACE (SPI) The AD9222 serial port interface allows the user to configure the converter for specific functions or operations through a structured register space provided inside the ADC. This gives the user added flexibility and customization, depending on the application. Addresses are accessed via the serial port and can be written to or read from via the port ...

Page 34

... If multiple SDIO pins share a common connection, care should be taken to ensure that proper V levels are met. Assuming the OH same load for each AD9222, Figure 83 shows the number of SDIO pins that can be connected together and the resulting V 1.800 1.795 1.790 1 ...

Page 35

... Minimum time for the SDIO pin to switch from an input to an output relative to the SCLK falling edge (not shown in Figure 84) Minimum time for the SDIO pin to switch from an output to an input relative to the SCLK rising edge (not shown in Figure 84) Rev Page DON’T CARE AD9222 DON’T CARE ...

Page 36

... Addresses that have values marked as 0 should be considered reserved and have a 0 written into their registers during power-up. DEFAULT VALUES When the AD9222 comes out of a reset, critical registers are preloaded with default values. These values are indicated in Table 16, where an X refers to an undefined feature. ...

Page 37

... Bit 5 Bit 4 Bit 3 Bit 2 Soft 1 1 Soft reset reset off 0 = off (default) (default) 8-bit Chip ID Bits 7:0 (AD9222 = 0x07), (default Data Data Channel Channel (default) (default off 0 = off Clock Clock Data Data ...

Page 38

... AD9222 Addr. (MSB) (Hex) Parameter Name Bit 7 Bit 6 14 output_mode LVDS ANSI-644 (default LVDS low power, (IEEE 1596.3 similar) 15 output_adjust output_phase user_patt1_lsb user_patt1_msb B15 B14 1B user_patt2_lsb user_patt2_msb B15 B14 21 serial_control LSB first off (default) 22 serial_ch_stat X X Bit 5 Bit 4 Bit 3 Bit Output ...

Page 39

... AD9222. An exposed continuous copper plane on the PCB should mate to the AD9222 exposed paddle, Pin 0. The copper plane should have several vias to achieve the lowest possible resistive thermal path for heat dissipation to flow through the bottom of the PCB. ...

Page 40

... Figure 90 to Figure 94). Figure 86 shows the typical bench characterization setup used to evaluate the ac performance of the AD9222 critical that the signal sources used for the analog input and clock have very low phase noise (<1 ps rms jitter) to realize the optimum performance of the converter ...

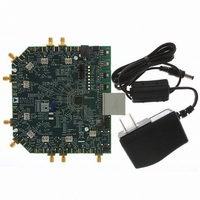

Page 41

... DEFAULT OPERATION AND JUMPER SELECTION SETTINGS The following is a list of the default and optional settings or modes allowed on the AD9222 Rev. A evaluation board. • POWER: Connect the switching power supply that is provided with the evaluation kit between a rated 100 240 V ac wall outlet and P701. ...

Page 42

... Figure 88. Example Filter Configured for16 MHz, Two-Pole Low-Pass Filter –20 –40 –60 –80 –100 –120 Figure 89. AD9222 FFT Example Results Using 16 MHz, Two-Pole Low-Pass Filter Applied to the AD8334 Outputs (f AD8334 = Maximum Gain Setting, Analog Input Signal = −1.03 dBFS, SNR = AD8334 data sheet Rev Page 680nH ...

Page 43

... Figure 90. Evaluation Board Schematic, DUT Analog Inputs Rev Page AD9222 05967-072 ...

Page 44

... AD9222 Figure 91. Evaluation Board Schematic, DUT Analog Inputs (Continued) Rev Page 05967-073 ...

Page 45

... CHB 30 D+C CHC 29 D−C CHC 28 D+D CHD 27 D−D CHD 26 FCO FCO+ 25 FCO− FCO 24 DCO+ DCO 23 DCO− DCO 22 D+E CHE 21 CHE D−E 20 D+F CHF 19 D−F CHF 18 D+G CHG 17 D−G CHG Rev Page AD9222 05967-074 AVDD_DUT CW GND ...

Page 46

... AD9222 GND RSET S10 6 VREF Figure 93. Evaluation Board Schematic, Clock Circuitry Rev Page 05967-075 ...

Page 47

... COM3 R508 274Ω C521 0.018µF C520 22pF L503 120nH 0.1µF C519 GND VG34 External Variable Gain Drive AD9222 05967-076 C535 C536 10µF 0.1µF R512 R511 10kΩ 10kΩ R509 274Ω C527 0.018µF C526 22pF ...

Page 48

... AD9222 C610 C609 10µF 0.1µF R605 AVDD_5V 10kΩ AVDD_5V C605 0.1µF R603 274Ω C602 0.018µF 0.1µF C601 AVDD_5V CW GND VG56 Variabl e Gain Circuit (0−1.0V DC) VG56 External Variable Gain Drive Figure 95. Evaluation Board Schematic, Optional DUT Analog Input Drive (Continued) R613 187Ω ...

Page 49

... OPTIONAL GREEN Figure 96. Evaluation Board Schematic, Power Supply Inputs and SPI Interface Circuitry C702 C703 0.1µF 0.1µF PICVCC 1 2 PICVCC GP1 3 4 GP1 GP0 5 6 GP0 MCLR/GP3 8 7 MCLR/GP3 9 10 Rev Page AD9222 05967-078 GND GND 1 1 GND GND ...

Page 50

... AD9222 Figure 97. Evaluation Board Layout, Primary Side Rev Page ...

Page 51

... Figure 98. Evaluation Board Layout, Ground Plane Rev Page AD9222 ...

Page 52

... AD9222 Figure 99. Evaluation Board Layout, Power Plane Rev Page ...

Page 53

... Figure 100. Evaluation Board Layout, Secondary Side (Mirrored Image) Rev Page AD9222 ...

Page 54

... AD9222 Table 17. Evaluation Board Bill of Materials (BOM) Qnty. per Reference Board Designator Item Device 1 1 AD9222-65EBZ PCB 2 118 C101, C102, C107, Capacitor C108, C109, C114, C115, C116, C121, C122, C123, C128, C201, C202, C207, C208, C209, C214, C215, C216, C221, C222, C223, C228, ...

Page 55

... SMD 402 120 nH, test freq 100 MHz, 5% tol, 150 mA Rev Page AD9222 Mfg. Mfg. Part Number Murata GRM1555C1H220JZ01D Rohm TCA1C106M8R Murata GRM188R61C105KA93D Murata GRM21BR71H104KA01L ...

Page 56

... AD9222 Qnty. per Reference Item Board Designator Device 26 32 L505, L506, L507, Resistor L508, L509, L510, L511, L512, L513, L514, L515, L516, L517, L518, L519, L520, L605, L606, L607, L608, L609, L610, L611, L612, L613, L614, L615, L616, L617, L618, L619, L620 ...

Page 57

... W, 1% tol 603 261 Ω, 1/ tol 402 240 Ω, 1/ tol 402 100 Ω, 1/ tol SMD LIGHT TOUCH, 100GE Rev Page AD9222 Mfg. Mfg. Part Number NIC NRC04F4990TRF Components Corp. NIC NRC04F1003TRF Components Corp. NIC NRC04F4121TRF Components Corp. Susumu RR0510R-49R9-D ...

Page 58

... ADP33339AKC-1.8-RL, 1.5 A, 1.8 V LDO regulator CP-64-3 AD8334ACPZ-REEL, ultralow noise precision dual VGA SOT-223 ADP3339AKC-5-RL7 SOT-223 ADP3339AKC-3.3-RL CP-64-3 AD9222BCPZ-65, octal, 12-bit, 50 MSPS serial LVDS 1.8 V ADC SOT-23 ADR510ARTZ, 1.0 V, precision low noise shunt voltage reference LFCSP AD9515BCPZ, 1.6 GHz CP-32-2 clock distribution IC ...

Page 59

... AD9222ABCPZRL7-40 −40°C to +85°C AD9222ABCPZ-50 −40°C to +85°C AD9222ABCPZRL7-50 −40°C to +85°C AD9222ABCPZ-65 −40°C to +85°C AD9222ABCPZRL7-65 −40°C to +85°C AD9222-65EBZ RoHS Compliant Part. 9.00 0.60 MAX 0.60 MAX 49 48 0.50 8.75 ...

Page 60

... AD9222 NOTES ©2006–2010 Analog Devices, Inc. All rights reserved. Trademarks and registered trademarks are the property of their respective owners. D05967-0-4/10(D) Rev Page ...