AD9222-65EBZ Analog Devices Inc, AD9222-65EBZ Datasheet - Page 27

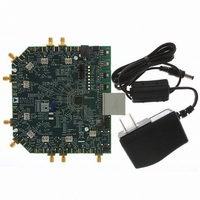

AD9222-65EBZ

Manufacturer Part Number

AD9222-65EBZ

Description

Octal 12 Bit, 65 MSPS Serial LVDS ADC EB

Manufacturer

Analog Devices Inc

Datasheet

1.AD9222ABCPZRL7-50.pdf

(60 pages)

Specifications of AD9222-65EBZ

Number Of Adc's

8

Number Of Bits

12

Sampling Rate (per Second)

65M

Data Interface

Serial

Inputs Per Adc

2 Single

Input Range

2 Vpp

Power (typ) @ Conditions

910mW @ 65MSPS

Voltage Supply Source

Single Supply

Operating Temperature

-40°C ~ 85°C

Utilized Ic / Part

AD9222

Kit Application Type

Data Converter

Application Sub Type

ADC

Features

Serial LVDS, Data And Frame Clock Outputs, 325MHz Full-power Analog Bandwidth

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

An example of the LVDS output using the ANSI-644 standard

(default) data eye and a time interval error (TIE) jitter histogram

with trace lengths less than 24 inches on standard FR-4 material is

shown in Figure 73 and Figure 74. Figure 75 and Figure 76 show

examples of trace lengths exceeding 24 inches on standard FR-4

material. Notice that the TIE jitter histogram reflects the decrease

of the data eye opening as the edge deviates from the ideal position.

It is the user’s responsibility to determine if the waveforms meet

the timing budget of the design when the trace lengths exceed

24 inches. Additional SPI options allow the user to further increase

the internal termination (increasing the current) of all eight outputs

in order to drive longer trace lengths (see Figure 77 and Figure 78).

Even though this produces sharper rise and fall times on the data

edges and is less prone to bit errors, the power dissipation of the

DRVDD supply increases when this option is used.

In cases that require increased driver strength to the DCO± and

FCO± outputs because of load mismatch, Register 0x15 allows

the user to increase the drive strength by 2×. To do this, set the

appropriate bit in Register 0x5. Note that this feature cannot be

used with Bit 4 and Bit 5 in Register 0x15. Bit 4 and Bit 5 take

precedence over this feature. See the Memory Map section for

more details.

Figure 73. Data Eye for LVDS Outputs in ANSI-644 Mode with Trace Lengths

–100

–200

–300

–400

–500

500

400

300

200

100

–1.5ns

–150ps

90

80

70

60

50

40

30

20

10

0

0

Less than 24 Inches on Standard FR-4, AD9222-50

EYE: ALL BITS

–1.0ns

–100ps

–0.5ns

–50ps

0ns

0ps

0.5ns

50ps

ULS: 12071/12071

1.0ns

100ps

150ps

1.5ns

Rev. D | Page 27 of 60

Figure 74. Data Eye for LVDS Outputs in ANSI-644 Mode with Trace Lengths

Figure 75. Data Eye for LVDS Outputs in ANSI-644 Mode with Trace Lengths

–100

–200

–300

–400

–500

–200

–400

–600

500

400

300

200

100

100

600

400

200

140

120

100

–200ps

–1.5ns

–150ps

90

80

70

60

50

40

30

20

10

80

60

40

20

–1.5ns

0

0

Greater than 24 Inches on Standard FR-4, AD9222-50

0

0

Less than 24 Inches on Standard FR-4, AD9222-65

EYE: ALL BITS

EYE: ALL BITS

–100ps

–1.0ns

–1.0ns

–100ps

–0.5ns

–0.5ns

–50ps

0ns

0ps

0ps

0ns

0.5ns

0.5ns

50ps

ULS: 9596/15596

ULS: 12067/12067

100ps

100ps

1.0ns

1.0ns

AD9222

1.5ns

150ps

200ps

1.5ns