SLCF2GBJIU-F STEC, SLCF2GBJIU-F Datasheet - Page 8

SLCF2GBJIU-F

Manufacturer Part Number

SLCF2GBJIU-F

Description

Manufacturer

STEC

Type

CompactFlashr

Datasheet

1.SLCF2GBJIU-F.pdf

(47 pages)

Specifications of SLCF2GBJIU-F

Density

2GByte

Operating Supply Voltage (typ)

3.3/5V

Operating Temperature (min)

-40C

Operating Temperature (max)

85C

Package Type

Not Required

Mounting

Socket

Pin Count

50

Operating Temperature Classification

Industrial

Operating Supply Voltage (min)

3.18/4.75V

Operating Supply Voltage (max)

3.465/5.25V

Programmable

Yes

Lead Free Status / RoHS Status

Compliant

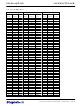

SLCFxxxJ(T2)(I)

SIGNAL DESCRIPTIONS

-OE

(PC Card Memory Mode)

-OE

(PC Card I/O Mode)

-OE

(True IDE Mode)

RDY/-BSY

(PC Card Memory Mode)

-IREQ

(PC Card I/O Mode)

INTRQ

(True IDE Mode)

A10-A0

(PC Card Memory Mode)

A10-A0

(PC Card I/O Mode)

A2-A0

(True IDE Mode)

-CE1, -CE2

(PC Card Memory Mode)

Card Enable

-CE1, -CE2

(PC Card I/O Mode)

Card Enable

-CS0, -CS1

(True IDE Mode)

Signal Name

Dir

O

I

I

I

14, 15, 16, 17,

8, 10, 11, 12,

18, 19, 20

27, 28, 29

7, 32

Pin

37

9

(continued)

This is an Output Enable strobe generated by the host interface. It is used

to read data from the card in Memory Mode and to read the CIS and

configuration registers.

In PC Card I/O Mode, this signal is used to read the CIS and configuration

registers.

To enable True IDE Mode, this input should be grounded by the host.

In Memory Mode this signal is set high when the card is ready to

accept a new data transfer operation and held low when the card is

busy. The host memory card socket must provide a pull-up resistor. At

power up and at reset, the RDY/-BSY signal is held low (busy) until

the card has completed its power up or reset function. No access of

any type should be made to the card during this time. The RDY/-BSY

signal is held high (disabled from being busy) whenever the following

condition is true: the card has been powered up with RESET

continuously disconnected or asserted high.

After the card has been configured for I/O operation, this signal is used as

the active low interrupt request. This line is strobed low to generate a pulse

mode interrupt or held low for a level mode interrupt.

In True IDE Mode, this signal is the active high interrupt request to the

host.

These address lines along with the -REG signal are used to select the

following: the I/O port address registers within the card, the memory

mapped port address registers within the card, a byte in the card’s

information structure and the card’s configuration control and status

registers.

This signal is the same as the PC Card Memory Mode signal.

In True IDE Mode only, A2:A0 are used to select the one of eight registers

in the Task File. The remaining address lines should be grounded.

These input signals are used both to select the card and to indicate to the

card whether a byte or a word operation is being performed. -CE2 always

accesses the odd byte of the word. -CE1 accesses the even byte or the odd

byte of the word depending on A0 and -CE2. A multiplexing scheme based

on A0, -CE1, -CE2 allows 8 bit hosts to access all data on D0-D7.

This signal is the same as the PC Card Memory Mode signal.

In the True IDE Mode, -CS0 is the chip select for the task file registers while

-CS2 is used to select the Alternate Status Register and the Device Control

Register.

Document Part Number 61000-02805-111 March 2005

Description

COMPACTFLASH

(continued)

Page 8