SLCF2GBJIU-F STEC, SLCF2GBJIU-F Datasheet - Page 9

SLCF2GBJIU-F

Manufacturer Part Number

SLCF2GBJIU-F

Description

Manufacturer

STEC

Type

CompactFlashr

Datasheet

1.SLCF2GBJIU-F.pdf

(47 pages)

Specifications of SLCF2GBJIU-F

Density

2GByte

Operating Supply Voltage (typ)

3.3/5V

Operating Temperature (min)

-40C

Operating Temperature (max)

85C

Package Type

Not Required

Mounting

Socket

Pin Count

50

Operating Temperature Classification

Industrial

Operating Supply Voltage (min)

3.18/4.75V

Operating Supply Voltage (max)

3.465/5.25V

Programmable

Yes

Lead Free Status / RoHS Status

Compliant

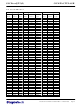

SLCFxxxJ(T2)(I)

SIGNAL DESCRIPTIONS

-CSEL

(PC Card Memory Mode)

-CSEL

(PC Card I/O Mode)

-CSEL

(True IDE Mode)

-REG

(PC Card Memory Mode)

Attribute Memory Select

-REG

(PC Card I/O Mode)

Not Used

(True IDE Mode)

WP

(PC Card Memory Mode)

Write Protect

-IOIS16

(PC Card I/O Mode)

-IOIS16

(True IDE Mode)

-INPACK

(PC Card Memory Mode)

-INPACK

(PC Card I/O Mode)

Input Acknowledge

Not Used

(True IDE Mode)

BVD1

(PC Card Memory Mode)

-STSCHG

(PC Card I/O Mode)

Status Changed

-PDIAG

(True IDE Mode)

Signal Name

I/O

Dir

O

O

I

I

Pin

39

44

24

43

46

(continued)

This signal is not used for this mode.

This signal is not used for this mode.

This internally pulled up signal is used to configure the card as a Master or

a Slave. When the pin is grounded, the card is configured as a Master.

When the pin is open, the card is configured as a Slave.

This signal is distinguishes between accesses to Common Memory (high)

and Register Attribute Memory (low).

The signal must also be active (low) during I/O Cycles when the I/O

address is on the bus.

This signal is not used in True IDE mode.

The card does not have a write protect switch; therefore, this signal is held

low after the completion of the reset initialization sequence.

A low signal indicates that a 16 bit or odd byte only operation can be

performed at the addressed port.

Not defined in IDE Mode.

This signal is not used in this mode.

The Input Acknowledge signal is asserted by the card when it is selected

and responding to an I/O read cycle at the address that is on the bus. The

host uses this signal to control the enable of any input data buffers between

the card and the host’s CPU.

This signal is not used in True IDE mode.

This signal is asserted high as since a battery is not used with this product.

This signal is asserted low to alert the host to changes in the RDY/-BSY

and Write Protect states. Its use is controlled by the Card Configuration

and Status Register.

In True IDE Mode, this input/output signal is the Pass Diagnostic signal in

the Master/Slave handshake protocol.

Document Part Number 61000-02805-111 March 2005

Description

COMPACTFLASH

(continued)

Page 9