EP2AGX95EF29I5N Altera, EP2AGX95EF29I5N Datasheet - Page 69

EP2AGX95EF29I5N

Manufacturer Part Number

EP2AGX95EF29I5N

Description

IC ARRIA II GX FPGA 95K 780FBGA

Manufacturer

Altera

Series

Arria II GXr

Datasheets

1.EP2AGX45CU17C6N.pdf

(96 pages)

2.EP2AGX45CU17C6N.pdf

(14 pages)

3.EP2AGX45CU17C6N.pdf

(692 pages)

4.EP2AGX45CU17C6N.pdf

(10 pages)

5.EP2AGX45CU17C6N.pdf

(88 pages)

6.EP2AGX95EF29I5N.pdf

(306 pages)

Specifications of EP2AGX95EF29I5N

Number Of Logic Elements/cells

89178

Number Of Labs/clbs

3747

Total Ram Bits

6679

Number Of I /o

372

Voltage - Supply

0.87 V ~ 0.93 V

Mounting Type

Surface Mount

Operating Temperature

-40°C ~ 100°C

Package / Case

780-FBGA

Family Name

Arria® II GX

Number Of Logic Blocks/elements

93674

# I/os (max)

372

Frequency (max)

500MHz

Operating Supply Voltage (typ)

900mV

Logic Cells

93674

Ram Bits

7025459.2

Operating Supply Voltage (min)

0.87V

Operating Supply Voltage (max)

0.93V

Operating Temp Range

-40C to 100C

Operating Temperature Classification

Industrial

Mounting

Surface Mount

Pin Count

780

Package Type

FC-FBGA

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Number Of Gates

-

Lead Free Status / Rohs Status

Compliant

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

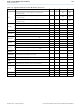

Chapter 1: Device Datasheet for Arria II Devices

Switching Characteristics

Table 1–45. PLL Specifications for Arria II GZ Devices (Part 2 of 2)

December 2010 Altera Corporation

t

f

t

t

t

t

t

t

t

t

f

Notes to

(1) This specification is limited in the Quartus II software by the I/O maximum frequency. The maximum I/O frequency is different for each I/O

(2) This specification is limited by the lower of the two: I/O F

(3) A high input jitter directly affects the PLL output jitter. To have low PLL output clock jitter, you must provide a clean clock source that is less

(4) F

(5) Peak-to-peak jitter with a probability level of 10

(6) The cascaded PLL specification is only applicable with the following condition:

(7) High bandwidth PLL settings are not supported in external feedback mode.

(8) External memory interface clock output jitter specifications use a different measurement method, which is available in

DLOCK

CLBW

PLL_PSERR

ARESET

INCCJ

OUTPJ_DC

OUTCCJ_DC

OUTPJ_IO

(8)

OUTCCJ_IO

(8)

CASC_OUTPJ_DC

(5),

DRIFT

Symbol

standard.

than 120 ps.

to the intrinsic jitter of the PLL, when an input jitter of 30 ps is applied. The external memory interface clock output jitter specifications use a

different measurement method and are available in

a. Upstream PLL: 0.59 Mhz Upstream PLL BW < 1 MHz

b. Downstream PLL: Downstream PLL BW > 2 MHz

page

REF

(6)

(3),

Table

is fIN/N when N = 1.

1–75.

(5),

(5)

(5),

(5)

(4)

1–45:

Time required to lock dynamically (after switchover or

reconfiguring any non-post-scale counters/delays)

PLL closed-loop low bandwidth

PLL closed-loop medium bandwidth

PLL closed-loop high bandwidth

Accuracy of PLL phase shift

Minimum pulse width on the areset signal

Input clock cycle to cycle jitter (F

Input clock cycle to cycle jitter (F

Period Jitter for dedicated clock output (F

Period Jitter for dedicated clock output (F

Cycle to Cycle Jitter for dedicated clock output

(F

Cycle to Cycle Jitter for dedicated clock output

(F

Period Jitter for clock output on regular I/O

(F

Period Jitter for clock output on regular I/O

(F

Cycle to Cycle Jitter for clock output on regular I/O

(F

Cycle to Cycle Jitter for clock output on regular I/O

(F

Period Jitter for dedicated clock output in cascaded PLLs

(F

Period Jitter for dedicated clock output in cascaded PLLs

(F

Frequency drift after PFDENA is disabled for duration of

100 us

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

≥ 100 MHz)

< 100 MHz)

< 100 MHz)

< 100 MHz)

< 100MHz)

≥ 100 MHz)

≥ 100 MHz)

≥100MHz)

Parameter

–12

(14 sigma, 99.99999999974404% confidence level). The output jitter specification applies

Table 1–63 on page

REF

REF

(7)

MAX

< 100 MHz)

≥ 100 MHz)

or F

OUT

OUT

OUT

≥ 100 MHz)

< 100 MHz)

of the PLL.

1–75.

Arria II Device Handbook Volume 3: Device Datasheet and Addendum

Min

—

—

—

—

—

10

—

—

—

—

—

—

—

—

—

—

—

—

—

Typ

0.3

1.5

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

4

±750

0.15

17.5

17.5

Max

±50

175

175

600

600

250

±10

—

—

—

—

60

60

25

1

Table 1–62 on

mUI (p-p)

mUI (p-p)

mUI (p-p)

mUI (p-p)

mUI (p-p)

UI (p-p)

ps (p-p)

ps (p-p)

ps (p-p)

ps (p-p)

ps (p-p)

ps (p-p)

MHz

MHz

MHz

Unit

ms

ps

ns

%

1–61