LTC4266CGW#PBF Linear Technology, LTC4266CGW#PBF Datasheet - Page 26

LTC4266CGW#PBF

Manufacturer Part Number

LTC4266CGW#PBF

Description

IC CTRLR IEEE 802.3AT 36-SSOP

Manufacturer

Linear Technology

Datasheet

1.LTC4266CGWPBF.pdf

(30 pages)

Specifications of LTC4266CGW#PBF

Controller Type

Ethernet Controller (IEEE 802.3)

Interface

I²C, 2-Wire Serial

Voltage - Supply

3.3V

Operating Temperature

0°C ~ 70°C

Mounting Type

Surface Mount

Package / Case

36-SSOP

Input Voltage

3.3V

Supply Current

-2.4mA

Digital Ic Case Style

SSOP

No. Of Pins

36

Duty Cycle (%)

60%

Uvlo

25V

Frequency

1MHz

Operating Temperature Range

0°C To +70°C

Msl

MSL 1 - Unlimited

Rohs Compliant

Yes

Operating Temperature (max)

70C

Operating Temperature (min)

0C

Pin Count

36

Mounting

Surface Mount

Package Type

SSOP

Screening Level

Commercial

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Current - Supply

-

Lead Free Status / Rohs Status

Compliant

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

LTC4266

APPLICATIONS INFORMATION

a perfect Kelvin connection because all four ports con-

trolled by the LTC4266 share the same sense trace, and

because the current through the trace (I

However, as the equation shows, the remaining error is a

small offset term.

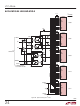

Figure 20 shows two LTC4266 chips controlling eight ports

(A though H). The ports are separated into two groups

of four; each has its own trace on the top PCB layer that

connects to the V

sub-circuit are effectively isolated from the U2 sub-circuit,

reducing the layout problem down to 4-port chunks; this

arrangement can be expanded for any number of ports.

Figure 21 shows an example of good 4-port layout. Each

0.25Ω sense resistor consists of four 1Ω resistors in

26

THIS TRACE PROVIDES V

BUT ALSO ACTS AS A KELVIN

SENSE LINE FOR PORTS A-D

EE

plane with a via. Currents from the U1

U1

LTC4266

EE

SENSE1

SENSE2

SENSE3

SENSE4

TO U1

V

EE

V

V

EE

Figure 20. Layout Strategy to Reduce Mutual Resistance

EE

COPPER FILL ON SURFACE LAYER

PLANE ON INNER LAYER

PORTS A THROUGH D

EE

) is not zero.

VIA

parallel. The four groups of resistors are arranged to

minimize the overlap in their current flows, which mini-

mizes mutual resistance. The horizontal slits cut in the

copper help to keep the currents separate. Wide copper

paths connect each group of resistors to the vias at the

center, so the resistance is very low.

Proper connection of the sense line is also important. In

Figure 21, U1 is not connected directly to the V

but is connected instead to a Kelvin sense trace that

leads to the sense resistor array. Similarly, the via at the

center of the sense resistor array has a matching hole

in the V

resistance of the four large vias from influencing the

current measurements.

BY KEEPING THESE COPPER FILLS SEPARATE ON

THE SURFACE, MUTUAL RESISTANCE BETWEEN

PORTS A-D AND E-H IS ELIMINATED

U2

LTC4266

SENSE1

SENSE2

SENSE3

SENSE4

V

EE

EE

plane. This arrangement prevents the mutual

PORTS E THROUGH H

VIA

R

SENSE

RETURN TO

V

EE

POWER SUPPLY

4266 F20

EE

plane

4266fb