LMX9838SB National Semiconductor, LMX9838SB Datasheet - Page 10

LMX9838SB

Manufacturer Part Number

LMX9838SB

Description

Manufacturer

National Semiconductor

Datasheet

1.LMX9838SB.pdf

(30 pages)

Specifications of LMX9838SB

Lead Free Status / Rohs Status

Compliant

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Part Number:

LMX9838SB

Manufacturer:

NS/国半

Quantity:

20 000

Company:

Part Number:

LMX9838SB/NOPB

Manufacturer:

NSC

Quantity:

560

Part Number:

LMX9838SB/NOPB

Manufacturer:

TI/德州仪器

Quantity:

20 000

Part Number:

LMX9838SBX

Manufacturer:

NS/国半

Quantity:

20 000

Company:

Part Number:

LMX9838SBX/NOPB

Manufacturer:

SMSC

Quantity:

101

www.national.com

Baud Rate

Flow Control

Parity

Stop Bits

Data Bits

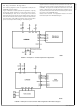

11.0 Functional Description

11.1 BASEBAND AND LINK MANAGEMENT

PROCESSORS

Baseband and Lower Link control functions are implemented

using a combination of National Semiconductor’s Com-

pactRISC 16-bit processor and the Bluetooth Lower Link

Controller. These processors operate from integrated ROM

memory and RAM and execute on-board firmware imple-

menting all Bluetooth functions.

11.1.1 Bluetooth Lower Link Controller

The integrated Bluetooth Lower Link Controller (LLC) com-

plies with the Bluetooth Specification version 2.0 and imple-

ments the following functions:

•

•

•

•

•

•

•

•

11.1.2 Bluetooth Upper Layer Stack

The integrated upper layer stack is prequalified and includes

the following protocol layers:

•

•

•

11.1.3 Profile Support

The on-chip application of the LMX9838 allows full stand-

alone operation, without any Bluetooth protocol layer neces-

sary outside the module. It supports the Generic Access

Profile (GAP), the Service Discovery Application Profile

(SDAP), and the Serial Port Profile (SPP).

The on-chip profiles can be used as interfaces to additional

profiles executed on the host. The LMX9838 includes a con-

figurable service database to answer requests with the pro-

files supported.

11.1.4 Application With Command Interface

The module supports automatic slave operation eliminating

the need for an external control unit. The implemented trans-

parent option enables the chip to handle incoming data raw,

Adaptive Frequency Hopping

Interlaced Scanning

Fast Connect

Support for 1, 3, and 5 slot packet types

79 Channel hop frequency generation circuitry

Fast frequency hopping at 1600 hops per second

Power management control

Access code correlation and slot timing recovery

L2CAP

RFComm

SDP

Item

2.4 to 921.6 kbits/s

RTS#/CTS# or None

Odd, Even, None

1,2

8

TABLE 6. UART Operation Modes

Range

10

without the need for packaging in a special format. The device

uses a pin to block unallowed connections. This pincode can

be fixed or dynamically set.

Acting as master, the application offers a simple but versatile

command interface for standard Bluetooth operation like in-

quiry, service discovery, or serial port connection. The

firmware supports up to seven slaves. Default Link Policy set-

tings and a specific master mode allow optimized configura-

tion for the application specific requirements. See Sec-

tion 14.0 Integrated Firmware.

11.1.5 Memory

The LMX9838 introduces 16 kB of combined system and

Patch RAM memory that can be used for data and/or code

upgrades of the ROM based firmware. Due to the flexible

startup used for the LMX9838 operating parameters like the

Bluetooth Device Address (BD_ADDR) are defined during

boot time. This allows reading out the parameters of an inter-

nal EEPROM or programming them directly over UART.

11.2 TRANSPORT PORT - UART

The LMX9838 provides one Universal Asynchronous Receiv-

er Transmitter (UART). The UART interface consists out of

Receive (RX), Transmit (TX), Ready-to-Send (RTS) and

Clear-to-Send signals. RTS and CTS are used for hardware

handshaking between the host and the LMX9838. Since the

LMX9838 acts as gateway between the bluetooth and the

UART interface, National Semiconductor recommends to use

the handshaking signals especially for transparent operation.

In case two signals are used CTS needs to be pulled to GND.

Please refer also to "LMX9838 Software User’s Guide" for

detailed information on 2-wire operation.

The UART interface supports formats of 8-bit data with or

without parity, with one or two stop bits. It can operate at

standard baud rates from 2400bits/s up to a maximum baud

rate of 921.6kbits/s. DMA transfers are supported to allow for

fast processor independent receive and transmit operation.

The UART baudrate is configured during startup by checking

option pins OP3, OP4 and OP5. Table 7 gives the correspon-

dence between the OP pins settings and the UART speed.

The UART offers wakeup from the power save modes via the

multi-input wakeup module. When the LMX9838 is in low

power mode, RTS# and CTS# can function as Host_WakeUp

and Bluetooth_WakeUp respectively. Table 6 represents the

operational modes supported by the firmware for implement-

ing the transport via the UART.

Either configured by option pins, NVS

RTS#/CTS#

None

1

8

Default at Power-Up