SAM3N2C Atmel Corporation, SAM3N2C Datasheet

SAM3N2C

Specifications of SAM3N2C

Related parts for SAM3N2C

SAM3N2C Summary of contents

Page 1

Features • Core ® ® – ARM Cortex -M3 revision 2.0 running MHz ® – Thumb -2 instruction – 24-bit SysTick Counter – Nested Vector Interrupt Controller • Pin-to-pin compatible with SAM7S legacy products (48- and ...

Page 2

... Kbytes 24 Kbytes SAM3N4C 256 Kbytes 24 Kbytes SAM3N2A 128 Kbytes 16 Kbytes SAM3N2B 128 Kbytes 16 Kbytes SAM3N2C 128 Kbytes 16 Kbytes SAM3N1A 64 Kbytes SAM3N1B 64 Kbytes SAM3N1C 64 Kbytes Notes: 1. Only two TC channels are accessible through the PIO. 2. Only three TC channels are accessible through the PIO. ...

Page 3

SAM3N Block Diagram Figure 2-1. SAM3N 100-pin version Block Diagram System Controller TST PCK0-PCK2 XIN XOUT WDT RC OSC 12/8/4 MHz OSC 32k XOUT32 ERASE VDDIO NRST PIOA VDDCORE URXD0 UTXD0 URXD1 UTXD1 RXD0 TXD0 SCK0 RTS0 CTS0 RXD1 ...

Page 4

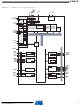

Figure 2-2. SAM3N 64-pin version Block Diagram System Controller TST PCK0-PCK2 XIN 3-20 MHz XOUT WDT RC OSC 12/8/4 MHz SUPC OSC 32k XOUT32 RC 32k ERASE VDDIO RSTC NRST PIOA VDDCORE URXD0 UTXD0 URXD1 UTXD1 RXD0 TXD0 SCK0 RTS0 ...

Page 5

Figure 2-3. SAM3N 48-pin version Block Diagram System Controller TST PCK0-PCK2 XIN XOUT WDT RC OSC 12/8/4 MHz OSC 32k XOUT32 ERASE VDDIO NRST PIOA VDDCORE URXD0 UTXD0 URXD1 UTXD1 RXD0 TXD0 SCK0 RTS0 CTS0 PWM[0:3] ADTRG AD[0..7] ADVREF 11011A–ATARM–04-Oct-10 ...

Page 6

Signal Description Table 3-1 Table 3-1. Signal Description List Signal Name Function VDDIO Peripherals I/O Lines Power Supply Voltage Regulator, ADC and DAC Power VDDIN Supply VDDOUT Voltage Regulator Output VDDPLL Oscillator and PLL Power Supply Power the core, ...

Page 7

Table 3-1. Signal Description List (Continued) Signal Name Function Flash and NVM Configuration Bits Erase ERASE Command NRST Microcontroller Reset TST Test Mode Select URXDx UART Receive Data UTXDx UART Transmit Data PA0 - PA31 Parallel IO Controller A PB0 ...

Page 8

Table 3-1. Signal Description List (Continued) Signal Name Function MISO Master In Slave Out MOSI Master Out Slave In SPCK SPI Serial Clock SPI_NPCS0 SPI Peripheral Chip Select 0 SPI_NPCS1 - SPI Peripheral Chip Select SPI_NPCS3 TWDx TWIx Two-wire Serial ...

Page 9

Package and Pinout SAM3N4/2/1 series is pin-to-pin compatible with SAM3S products. Furthermore SAM3N4/2/1 devices have new functionalities referenced in italic 4.1 SAM3N4/2/1C Package and Pinout 4.1.1 100-lead LQFP Package Outline Figure 4-1. 4.1.2 100-ball LFBGA Package Outline The 100-Ball ...

Page 10

LQFP Pinout Table 4-1. 100-lead LQFP SAM3N4/2/1C Pinout 1 ADVREF 26 2 GND 27 3 PB0/AD4 28 4 PC29/AD13 29 5 PB1/AD5 30 6 PC30/AD14 31 7 PB2/AD6 32 8 PC31/AD15 33 9 PB3/AD7 34 10 VDDIN 35 ...

Page 11

LFBGA Pinout Table 4-2. 100-ball LFBGA SAM3N4/2/1C Pinout A1 PB1/AD5 A2 PC29 A3 VDDIO A4 PB9/PGMCK/XIN A5 PB8/XOUT C10 A6 PB13/DAC0 A7 DDP/PB11 A8 DDM/PB10 A9 TMS/SWDIO/PB6 A10 JTAGSEL B1 PC30 B2 ADVREF B3 GNDANA B4 PB14/DAC1 B5 ...

Page 12

SAM3N4/2/1B Package and Pinout Figure 4-3. Figure 4-4. SAM3N 12 Orientation of the 64-pad QFN Package TOP VIEW Orientation of the 64-lead LQFP Package ...

Page 13

LQFP and QFN Pinout 64-pin version SAM3N devices are pin-to-pin compatible with SAM3S products. Furthermore, SAM3N products have new functionalities shown in italic in Table 4-3. 64-pin SAM3N4/2/1B Pinout 1 ADVREF 2 GND 3 PB0/AD4 4 PB1AD5 5 ...

Page 14

SAM3N4/2/1A Package and Pinout Figure 4-5. Figure 4-6. SAM3N 14 Orientation of the 48-pad QFN Package TOP VIEW Orientation of the 48-lead LQFP Package ...

Page 15

LQFP and QFN Pinout Table 4-4. 48-pin SAM3N4/2/1A Pinout 1 ADVREF 13 2 GND 14 3 PB0/AD4 15 4 PB1/AD5 16 5 PB2/AD6 17 6 PB3/AD7 18 7 VDDIN 19 8 VDDOUT 20 9 PA17/PGMD5/AD0 21 10 PA18/PGMD6/AD1 ...

Page 16

Power Considerations 5.1 Power Supplies The SAM3N product has several types of power supply pins: • VDDCORE pins: Power the core, including the processor, the embedded memories and the peripherals. Voltage ranges from 1.62V to 1.95V. • VDDIO pins: ...

Page 17

Figure 5-1. Figure 5-2. Note: Figure 5-3 Since the PIO state is preserved when in backup mode, any free PIO line can be used to switch off the external regulator by driving the PIO line at low level (PIO is ...

Page 18

Figure 5-3. 5.4 Active Mode Active mode is the normal running mode with the core clock running from the fast RC oscillator, the main crystal oscillator or the PLL. The power management controller can be used to adapt the frequency ...

Page 19

Supply Monitor alarm • RTC alarm • RTT alarm 5.5.2 Wait Mode The purpose of the wait mode is to achieve very low power consumption while maintaining the whole device in a powered state for a startup time of ...

Page 20

Low Power Mode Summary Table The modes detailed above are the main low power modes. Each part can be set off sep- arately and wake up sources can be individually configured. of the configurations of the ...

Page 21

Wake-up Sources The wake-up events allow the device to exit backup mode. When a wake-up event is detected, the Supply Controller performs a sequence which automatically reenables the core power sup- ply and the SRAM power supply, if they ...

Page 22

Fast Start-Up The SAM3N allows the processor to restart in a few microseconds while the processor is in wait mode. A fast start up can occur upon detection of a low level on one of the 19 wake-up inputs ...

Page 23

Input/Output Lines The SAM3N has several kinds of input/output (I/O) lines such as general purpose I/Os (GPIO) and system I/Os. GPIOs can have alternate functionality due to multiplexing capabilities of the PIO controllers. The same PIO line can be ...

Page 24

Table 6-1. System I/O Configuration Pin List. SYSTEM_IO Default function bit number after reset 12 ERASE 7 TCK/SWCLK 6 TMS/SWDIO 5 TDO/TRACESWO 4 TDI - PA7 - PA8 - PB9 - PB8 Notes PB12 is used as PIO ...

Page 25

Test Pin The TST pin is used for JTAG Boundary Scan Manufacturing Test or Fast Flash programming mode of the SAM3N series. The TST pin integrates a permanent pull-down resistor of about 15 kΩ to GND, so that it ...

Page 26

Memories 7.1 Product Mapping Figure 7-1. SAM3N4/2/1 Product Mapping Code 0x00000000 0x00000000 Boot Memory 0x00400000 Internal Flash 1 MByte 0x20000000 0x00800000 bit band 0x20100000 Internal ROM region 0x00C00000 Reserved 0x22000000 0x1FFFFFFF 0x24000000 0x40000000 0x60000000 0xA0000000 0xE0000000 0xFFFFFFFF SAM3N 26 ...

Page 27

Embedded Memories 7.2.1 Internal SRAM The SAM3N4 product embeds a total of 24-Kbytes high-speed SRAM. The SAM3N2 product embeds a total of 16-Kbytes high-speed SRAM. The SAM3N1 product embeds a total of 8-Kbytes high-speed SRAM. The SRAM is accessible ...

Page 28

Flash Speed The user needs to set the number of wait states depending on the frequency used. For more details, refer to the AC Characteristics sub section in the “Electrical Characteristics” section. 7.2.3.5 Lock Regions Several lock bits used ...

Page 29

Fast Flash Programming Interface The Fast Flash Programming Interface allows programming the device through either a serial JTAG interface or through a multiplexed fully-handshaked parallel port. It allows gang program- ming with market-standard industrial programmers. The FFPI supports read, ...

Page 30

System Controller The System Controller is a set of peripherals, which allow handling of key elements of the sys- tem, such as power, resets, clocks, time, interrupts, watchdog, etc... See the System Controller block diagram in SAM3N 30 Figure ...

Page 31

Figure 8-1. System Controller Block Diagram VDDIO Zero-Power Power-on Reset Supply Monitor (Backup) WKUP0 - WKUP15 General Purpose Backup Registers SLCK SLCK XIN32 Xtal 32 kHz Oscillator XOUT32 Embedded 32 kHz RC Oscillator Backup Power Supply core_nreset NRST FSTT0 - ...

Page 32

System Controller and Peripheral Mapping Please refer to All the peripherals are in the bit band region and are mapped in the bit band alias region. 8.2 Power-on-Reset, Brownout and Supply Monitor The SAM3N embeds three features to monitor, ...

Page 33

Peripherals 9.1 Peripheral Identifiers Table 9-1 for the control of the peripheral interrupt with the Nested Vectored Interrupt Controller and for the control of the peripheral clock with the Power Management Controller. Table 9-1. Peripheral Identifiers Instance ID Instance ...

Page 34

APB/AHB Bridge The SAM3N4/2/1 product embeds one peripheral bridge: The peripherals of the bridge are clocked by MCK. 9.3 Peripheral Signal Multiplexing on I/O Lines The SAM3N product features 2 PIO controllers (48-pin and 64-pin version PIO ...

Page 35

PIO Controller A Multiplexing Table 9-2. Multiplexing on PIO Controller A (PIOA) I/O Line Peripheral A Peripheral B PA0 PWM0 PA1 PWM1 PA2 PWM2 PA3 TWD0 PA4 TWCK0 PA5 RXD0 PA6 TXD0 PA7 RTS0 PA8 CTS0 PA9 URXD0 PA10 ...

Page 36

PIO Controller B Multiplexing Table 9-3. Multiplexing on PIO Controller B (PIOB) I/O Line Peripheral A Peripheral B PB0 PWM0 PB1 PWM1 PB2 URXD1 NPCS2 PB3 UTXD1 PB4 TWD1 PWM2 PB5 TWCK1 PB6 PB7 PB8 PB9 PB10 PB11 PB12 ...

Page 37

PIO Controller C Multiplexing I/O Line Peripheral A Peripheral B PC0 PC1 PC2 PC3 PC4 NPCS1 PC5 PC6 PC7 NPCS2 PC8 PC9 PC10 PC11 PC12 PC13 PC14 PC15 PC16 PC17 PC18 PC19 PC20 PC21 PC22 PC23 PC24 PC25 TCLK3 ...

Page 38

SAM3N 38 11011A–ATARM–04-Oct-10 ...

Page 39

ARM Cortex M3 Processor 10.1 About this section This section provides the information required for application and system-level software devel- opment. It does not provide information on debug components, features, or operation. This material is for microcontroller software ...

Page 40

Figure 10-1. Typical Cortex-M3 Implementation The Cortex-M3 processor is built on a high-performance processor core, ...

Page 41

System level interface The Cortex-M3 processor provides multiple interfaces using AMBA speed, low latency memory accesses. It supports unaligned data accesses and implements atomic bit manipulation that enables faster peripheral controls, system spinlocks and thread-safe Boolean data handling. 10.3.2 ...

Page 42

Programmers model This section describes the Cortex-M3 programmers model. In addition to the individual core reg- ister descriptions, it contains information about the processor modes and privilege levels for software execution and stacks. 10.4.1 Processor mode and privilege levels ...

Page 43

In Thread mode, the CONTROL register controls whether the processor uses the main stack or the process stack, see uses the main stack. The options for processor operations are: Table 10-1. Processor mode Thread Handler 1. 10.4.3 Core registers The ...

Page 44

Table 10-2. Name R0-R12 MSP PSP LR PC PSR ASPR IPSR EPSR PRIMASK FAULTMASK BASEPRI CONTROL 1. 2. 10.4.3.1 General-purpose registers R0-R12 are 32-bit general-purpose registers for data operations. 10.4.3.2 Stack Pointer The Stack Pointer (SP) is register R13. In ...

Page 45

Program Counter The Program Counter (PC) is register R15. It contains the current program address. Bit[0] is always 0 because instruction fetches must be halfword aligned. On reset, the processor loads the PC with the value of the reset ...

Page 46

Program Status Register The Program Status Register (PSR) combines: • Application Program Status Register (APSR) • Interrupt Program Status Register (IPSR) • Execution Program Status Register (EPSR). These registers are mutually exclusive bitfields in the 32-bit PSR. The bit ...

Page 47

The PSR bit assignments are Access these registers individually combination of any two or all three registers, using the register name as an argument to the MSR ...

Page 48

C Carry or borrow flag add operation did not result in a carry bit or subtract operation resulted in a borrow bit 1 = add operation resulted in a carry bit or subtract operation did not result ...

Page 49

Execution Program Status Register The EPSR contains the Thumb state bit, and the execution state bits for either the: • If-Then (IT) instruction • Interruptible-Continuable Instruction (ICI) field for an interrupted load multiple or store multiple instruction. See the ...

Page 50

Priority Mask Register The PRIMASK register prevents activation of all exceptions with configurable priority. See the register summary • PRIMASK effect 1 = prevents the activation of ...

Page 51

Base Priority Mask Register The BASEPRI register defines the minimum priority for exception processing. When BASEPRI is set to a nonzero value, it prevents the activation of all exceptions with same or lower priority level as the BASEPRI value. ...

Page 52

CONTROL register The CONTROL register controls the stack used and the privilege level for software execution when the processor is in Thread mode. See the register summary in its attributes. The bit assignments are ...

Page 53

Exceptions and interrupts The Cortex-M3 processor supports interrupts and system exceptions. The processor and the Nested Vectored Interrupt Controller (NVIC) prioritize and handle all exceptions. An exception changes the normal flow of software control. The processor uses handler mode ...

Page 54

CMSIS mapping of the Cortex-M3 NVIC registers” on page 151 • “NVIC programming hints” on page SAM3N 54 163. 11011A–ATARM–04-Oct-10 ...

Page 55

Memory model This section describes the processor memory map, the behavior of memory accesses, and the bit-banding features. The processor has a fixed memory map that provides up to 4GB of addressable memory. The memory map is: The regions ...

Page 56

Normal The processor can re-order transactions for efficiency, or perform speculative reads. 10.5.1.2 Device The processor preserves transaction order relative to other transactions to Device or Strongly- ordered memory. 10.5.1.3 Strongly-ordered The processor preserves transaction order relative to all ...

Page 57

Means that accesses are observed in program order, that is always observed before A2. 10.5.3 Behavior of memory accesses The behavior of accesses to each region in the memory map is: Table 10-4. Address range 0x00000000- 0x1FFFFFFF ...

Page 58

Table 10-5. Address range 0xA0000000- 0xBFFFFFFF 0xC0000000- 0xDFFFFFFF 0xE0000000- 0xE00FFFFF 0xE0100000- 0xFFFFFFFF 1. 2. 10.5.4 Software ordering of memory accesses The order of instructions in the program flow does not always guarantee the order of the corre- sponding memory transactions. ...

Page 59

Memory map switching. If the system contains a memory map switching mechanism, use a DSB instruction after switching the memory map in the program. This ensures subsequent instruction execution uses the updated memory map. • Dynamic exception priority change. ...

Page 60

Bit_word_offset is the position of the target bit in the bit-band memory region. • Bit_word_addr is the address of the word in the alias memory region that maps to the targeted bit. • ...

Page 61

Reading a word in the alias region: • 0x00000000 indicates that the targeted bit in the bit-band region is set to zero • 0x00000001 indicates that the targeted bit in the bit-band region is set to 1 10.5.5.2 Directly accessing ...

Page 62

LDREXH and STREXH • the byte instructions LDREXB and STREXB. Software must use a Load-Exclusive instruction with the corresponding Store-Exclusive instruction. To perform a guaranteed read-modify-write of a memory location, software must: • Use a Load-Exclusive ...

Page 63

Programming hints for the synchronization primitives ANSI C cannot directly generate the exclusive access instructions. Some C compilers provide intrinsic functions for generation of these instructions: Table 10-8. Instruction LDREX, LDREXH, or LDREXB STREX, STREXH, or STREXB CLREX The ...

Page 64

Execution restarts as privileged execution in Thread mode. 10.6.2.2 Non Maskable Interrupt (NMI) A non maskable interrupt (NMI) can be signalled by a peripheral or triggered by software. This is the ...

Page 65

Interrupt (IRQ) A interrupt, or IRQ exception signalled by a peripheral, or generated by a software request. All interrupts are asynchronous to instruction execution. In the system, peripherals use interrupts to communicate with the processor. Table 10-9. ...

Page 66

Clear-enable Registers” on page For more information about hard faults, memory management faults, bus faults, and usage faults, see 10.6.3 Exception handlers The processor handles exceptions using: 10.6.3.1 Interrupt Service Routines (ISRs) Interrupts IRQ0 to IRQ32 are the ...

Page 67

Figure 10-3. Vector table On system reset, the vector table is fixed at address 0x00000000. Privileged software can write to the VTOR to relocate the vector table start address to a different memory location, in the range 0x00000080 to 0x3FFFFF80, ...

Page 68

Configurable priority values are in the range 0-15. This means that the Reset, Hard fault, and NMI exceptions, with fixed negative priority values, always have higher priority than any other exception. For example, assigning a higher priority value to IRQ[0] ...

Page 69

Tail-chaining This mechanism speeds up exception servicing. On completion of an exception handler, if there is a pending exception that meets the requirements for exception entry, the stack pop is skipped and control transfers to the new exception handler. ...

Page 70

If no higher priority exception occurs during exception entry, the processor starts executing the exception handler and automatically changes the status of the corresponding pending interrupt to active. If another higher priority exception occurs during exception entry, the processor starts ...

Page 71

BX instruction • attempting to execute an instruction from a memory region marked as Non-Executable 10.7.1 Fault types Table 10-11 tus register, and ...

Page 72

A fault handler causes a fault with the same or lower priority as the fault it is servicing. This is because the handler for the new fault cannot preempt the currently executing fault handler. • An exception handler causes ...

Page 73

The SLEEPDEEP bit of the SCR selects which sleep mode is used, see ter” on page Modes” in the PMC section of the datasheet. This section describes the mechanisms for entering sleep mode, and the conditions for waking up from ...

Page 74

In addition, if the SEVONPEND bit in the SCR is set to 1, any new pending interrupt triggers an event and wakes up the processor, even if the interrupt is disabled or has insufficient priority to cause exception entry. For ...

Page 75

Instruction set summary The processor implements a version of the Thumb instruction set. ported instructions. In Table • angle brackets, <>, enclose alternative forms of the operand • braces, {}, enclose optional operands • the Operands column is not ...

Page 76

Table 10-13. Cortex-M3 instructions (Continued) Mnemonic ISB IT LDM LDMDB, LDMEA LDMFD, LDMIA LDR LDRB, LDRBT LDRD LDREX LDREXB LDREXH LDRH, LDRHT LDRSB, LDRSBT LDRSH, LDRSHT LDRT LSL, LSLS LSR, LSRS MLA MLS MOV, MOVS MOVT MOVW, MOV MRS MSR ...

Page 77

Table 10-13. Cortex-M3 instructions (Continued) Mnemonic RBIT REV REV16 REVSH ROR, RORS RRX, RRXS RSB, RSBS SBC, SBCS SBFX SDIV SEV SMLAL SMULL SSAT STM STMDB, STMEA STMFD, STMIA STR STRB, STRBT STRD STREX STREXB STREXH STRH, STRHT STRT SUB, ...

Page 78

Table 10-13. Cortex-M3 instructions (Continued) Mnemonic TEQ TST UBFX UDIV UMLAL UMULL USAT UXTB UXTH WFE WFI 10.10 Intrinsic functions ANSI cannot directly access some Cortex-M3 instructions. This section describes intrinsic func- tions that can generate these instructions, provided by ...

Page 79

The CMSIS also provides a number of functions for accessing the special registers using MRS and MSR instructions: Table 10-15. CMSIS intrinsic functions to access the special registers Special register PRIMASK FAULTMASK BASEPRI CONTROL MSP PSP 10.11 About the instruction ...

Page 80

Bit[0] of any address you write to the PC with a BX, BLX, LDM, LDR, or POP instruction must be 1 for correct execution, because this bit indicates the required instruction set, and the Cortex-M3 processor only supports Thumb instructions. ...

Page 81

LSR #n ROR #n RRX - If you omit the shift, or specify LSL #0, the instruction uses the value in Rm. If you specify a shift, the shift is applied to the value in Rm, and the resulting 32-bit ...

Page 82

LSR Logical shift right by n bits moves the left-hand 32-n bits of the register Rm, to the right by n places, into the right-hand 32-n bits of the result. And it sets the left-hand n bits of the ...

Page 83

ROR Rotate right by n bits moves the left-hand 32-n bits of the register Rm, to the right by n places, into the right-hand 32-n bits of the result. And it moves the right-hand n bits of the register ...

Page 84

All other load and store instructions generate a usage fault exception if they perform an unaligned access, and therefore their accesses must be address aligned. For more information about usage faults see Unaligned accesses are usually slower than aligned accesses. ...

Page 85

This section describes: • “The condition flags” • “Condition code suffixes” 10.11.7.1 The condition flags The APSR contains the following condition flags For more information about the APSR see A carry occurs: • if the result ...

Page 86

Table 10-16. Condition code suffixes (Continued) Suffix 10.11.7.3 Absolute value The example below shows the use of a conditional instruction to find the absolute value of a number ABS(R1). MOVS ...

Page 87

Memory access instructions Table 10-17 Table 10-17. Memory access instructions Mnemonic ADR CLREX LDM{mode} LDR{type} LDR{type} LDR{type}T LDR LDREX{type} POP PUSH STM{mode} STR{type} STR{type} STR{type}T STREX{type} 11011A–ATARM–04-Oct-10 shows the memory access instructions: Brief description Load PC-relative address Clear Exclusive ...

Page 88

ADR Load PC-relative address. 10.12.1.1 Syntax ADR{cond} Rd, label where: cond Rd label 10.12.1.2 Operation ADR determines the address by adding an immediate value to the PC, and writes the result to the destination register. ADR produces position-independent code, ...

Page 89

LDR and STR, immediate offset Load and Store with immediate offset, pre-indexed immediate offset, or post-indexed immediate offset. 10.12.2.1 Syntax op{type}{cond} Rt, [Rn {, #offset}] op{type}{cond} Rt, [Rn, #offset]! op{type}{cond} Rt, [Rn], #offset opD{cond} Rt, Rt2, [Rn {, #offset}] ...

Page 90

Post-indexed addressing The address obtained from the register Rn is used as the address for the memory access. The offset value is added to or subtracted from the address, and written back into the register Rn. The ...

Page 91

Examples LDR R8, [R10] LDRNE R2, [R5, #960]! STR R2, [R9,#const-struc] STRH R3, [R4], #4 LDRD R8, R9, [R3, #0x20] STRD R0, R1, [R8], #-16 11011A–ATARM–04-Oct-10 ; Loads R8 from the address in R10. ; Loads (conditionally) R2 from ...

Page 92

LDR and STR, register offset Load and Store with register offset. 10.12.3.1 Syntax op{type}{cond} Rt, [Rn LSL #n}] where: op LDR STR type cond LSL #n 10.12.3.2 Operation LDR ...

Page 93

Condition flags These instructions do not change the flags. 10.12.3.5 Examples STR R0, [R5, R1] LDRSB R0, [R5, R1, LSL #1] ; Read byte value from an address equal to STR R0, [R1, R2, LSL #2] ; Stores R0 ...

Page 94

LDR and STR, unprivileged Load and Store with unprivileged access. 10.12.4.1 Syntax op{type}T{cond} Rt, [Rn {, #offset}] where: op LDR STR type is one of cond Rt Rn offset 10.12.4.2 Operation These load and ...

Page 95

LDR, PC-relative Load register from memory. 10.12.5.1 Syntax LDR{type}{cond} Rt, label LDRD{cond} Rt, Rt2, label where: type cond Rt Rt2 label 10.12.5.2 Operation LDR loads a register with a value from a PC-relative memory ...

Page 96

IT block. 10.12.5.4 Condition flags These ...

Page 97

LDM and STM Load and Store Multiple registers. 10.12.6.1 Syntax op{addr_mode}{cond} Rn{!}, reglist where: op LDM STM addr_mode IA DB cond present the final address, that is loaded from or stored to, is written ...

Page 98

The accesses happen in order of decreasing register numbers, with the highest numbered regis- ter using the highest memory address and the lowest number register using the lowest memory address. If the writeback suffix is specified, the value of Rn ...

Page 99

PUSH and POP Push registers onto, and pop registers off a full-descending stack. 10.12.7.1 Syntax PUSH{cond} reglist POP{cond} reglist where: cond reglist It must be comma separated if it contains more than one register or register range. PUSH and ...

Page 100

LDREX and STREX Load and Store Register Exclusive. 10.12.8.1 Syntax LDREX{cond} Rt, [Rn {, #offset}] STREX{cond} Rd, Rt, [Rn {, #offset}] LDREXB{cond} Rt, [Rn] STREXB{cond} Rd, Rt, [Rn] LDREXH{cond} Rt, [Rn] STREXH{cond} Rd, Rt, [Rn] where: cond Rd Rt ...

Page 101

Condition flags These instructions do not change the flags. 10.12.8.5 Examples MOV R1, #0x1 try LDREX R0, [LockAddr] CMP R0, #0 ITT EQ STREXEQ R0, R1, [LockAddr] CMPEQ R0, #0 BNE try .... 11011A–ATARM–04-Oct-10 ; Initialize the ‘lock taken’ ...

Page 102

CLREX Clear Exclusive. 10.12.9.1 Syntax CLREX{cond} where: cond 10.12.9.2 Operation Use CLREX to make the next STREX, STREXB, or STREXH instruction write 1 to its destination register and fail to perform the store useful in exception handler ...

Page 103

General data processing instructions Table 10-20 Table 10-20. Data processing instructions Mnemonic ADC ADD ADDW AND ASR BIC CLZ CMN CMP EOR LSL LSR MOV MOVT MOVW MVN ORN ORR RBIT REV REV16 REVSH ROR 11011A–ATARM–04-Oct-10 shows the data ...

Page 104

Table 10-20. Data processing instructions (Continued) Mnemonic RRX RSB SBC SUB SUBW TEQ TST SAM3N 104 Brief description Rotate Right with Extend Reverse Subtract Subtract with Carry Subtract Subtract Test Equivalence Test See “ASR, LSL, LSR, ROR, and RRX” on ...

Page 105

ADD, ADC, SUB, SBC, and RSB Add, Add with carry, Subtract, Subtract with carry, and Reverse Subtract. 10.13.1.1 Syntax op{S}{cond} {Rd,} Rn, Operand2 op{cond} {Rd,} Rn, #imm12 where: op ADD ADC SUB SBC RSB S result of the operation, ...

Page 106

Rd can be SP only in ADD and SUB, and only with the additional restrictions: – Rn must also be SP – any shift in Operand2 must be limited to a maximum of 3 bits using LSL • Rn ...

Page 107

Multiword arithmetic examples 10.13.1.7 64-bit addition The example below shows two instructions that add a 64-bit integer contained in R2 and R3 to another 64-bit integer con- tained in R0 and R1, and place the result in R4 and ...

Page 108

AND, ORR, EOR, BIC, and ORN Logical AND, OR, Exclusive OR, Bit Clear, and OR NOT. 10.13.2.1 Syntax op{S}{cond} {Rd,} Rn, Operand2 where: op AND ORR EOR BIC ORN S result of the operation, see cond Rd Rn Operand2 ...

Page 109

Examples AND R9, R2, #0xFF00 ORREQ R2, R0, R5 ANDS R9, R8, #0x19 EORS R7, R11, #0x18181818 BIC R0, R1, #0xab ORN R7, R11, R14, ROR #4 ORNS R7, R11, R14, ASR #32 11011A–ATARM–04-Oct-10 SAM3N 109 ...

Page 110

ASR, LSL, LSR, ROR, and RRX Arithmetic Shift Right, Logical Shift Left, Logical Shift Right, Rotate Right, and Rotate Right with Extend. 10.13.3.1 Syntax op{S}{cond} Rd, Rm, Rs op{S}{cond} Rd, Rm, #n RRX{S}{cond} Rd, Rm where: op ASR LSL ...

Page 111

C flag is updated to the last bit shifted out, except when the shift length is 0, see Operations” on page 10.13.3.5 Examples ASR R7, R8 Arithmetic shift right by 9 bits LSLS R1, R2, #3 ...

Page 112

CLZ Count Leading Zeros. 10.13.4.1 Syntax CLZ{cond} Rd, Rm where: cond Rd Rm 10.13.4.2 Operation The CLZ instruction counts the number of leading zeros in the value in Rm and returns the result in Rd. The result value is ...

Page 113

CMP and CMN Compare and Compare Negative. 10.13.5.1 Syntax CMP{cond} Rn, Operand2 CMN{cond} Rn, Operand2 where: cond Rn Operand2 details of the options. 10.13.5.2 Operation These instructions compare the value in a register with Operand2. They update the condition ...

Page 114

MOV and MVN Move and Move NOT. 10.13.6.1 Syntax MOV{S}{cond} Rd, Operand2 MOV{cond} Rd, #imm16 MVN{S}{cond} Rd, Operand2 where: S result of the operation, see cond Rd Operand2 details of the options. imm16 10.13.6.2 Operation The MOV instruction copies ...

Page 115

PC is ignored • a branch occurs to the address created by forcing bit[0] of that value to 0. Though it is possible to use MOV as a branch instruction, ARM strongly ...

Page 116

MOVT Move Top. 10.13.7.1 Syntax MOVT{cond} Rd, #imm16 where: cond Rd imm16 10.13.7.2 Operation MOVT writes a 16-bit immediate value, imm16, to the top halfword, Rd[31:16], of its destination register. The write does not affect Rd[15:0]. The MOV, MOVT ...

Page 117

REV, REV16, REVSH, and RBIT Reverse bytes and Reverse bits. 10.13.8.1 Syntax op{cond} Rd, Rn where: op REV REV16 Reverse byte order in each halfword independently. REVSH Reverse byte order in the bottom halfword, and sign extend to 32 ...

Page 118

TST and TEQ Test bits and Test Equivalence. 10.13.9.1 Syntax TST{cond} Rn, Operand2 TEQ{cond} Rn, Operand2 where: cond Rn Operand2 details of the options. 10.13.9.2 Operation These instructions test the value in a register against Operand2. They update the ...

Page 119

Multiply and divide instructions Table 10-21 Table 10-21. Multiply and divide instructions Mnemonic MLA MLS MUL SDIV SMLAL SMULL UDIV UMLAL UMULL 11011A–ATARM–04-Oct-10 shows the multiply and divide instructions: Brief description Multiply with Accumulate, 32-bit result Multiply and Subtract, ...

Page 120

MUL, MLA, and MLS Multiply, Multiply with Accumulate, and Multiply with Subtract, using 32-bit operands, and pro- ducing a 32-bit result. 10.14.1.1 Syntax MUL{S}{cond} {Rd,} Rn Multiply MLA{cond} Rd, Rn, Rm, Ra MLS{cond} Rd, Rn, Rm, Ra ...

Page 121

UMULL, UMLAL, SMULL, and SMLAL Signed and Unsigned Long Multiply, with optional Accumulate, using 32-bit operands and pro- ducing a 64-bit result. 10.14.2.1 Syntax op{cond} RdLo, RdHi, Rn, Rm where: op UMULL Unsigned Long Multiply. UMLAL Unsigned Long Multiply, ...

Page 122

SDIV and UDIV Signed Divide and Unsigned Divide. 10.14.3.1 Syntax SDIV{cond} {Rd,} Rn, Rm UDIV{cond} {Rd,} Rn, Rm where: cond 10.14.3.2 Operation SDIV performs a signed integer division of the value the value ...

Page 123

Saturating instructions This section describes the saturating instructions, SSAT and USAT. 10.15.1 SSAT and USAT Signed Saturate and Unsigned Saturate to any bit position, with optional shift before saturating. 10.15.1.1 Syntax op{cond} Rd, # shift #s} where: ...

Page 124

Restrictions Do not use SP and do not use PC 10.15.1.4 Condition flags These instructions do not affect the condition code flags. If saturation occurs, these instructions set the Q flag to 1. 10.15.1.5 Examples SSAT R7, #16, R7, ...

Page 125

Bitfield instructions Table 10-22 Table 10-22. Packing and unpacking instructions Mnemonic BFC BFI SBFX SXTB SXTH UBFX UXTB UXTH 11011A–ATARM–04-Oct-10 shows the instructions that operate on adjacent sets of bits in registers or bitfields: Brief description Bit Field Clear ...

Page 126

BFC and BFI Bit Field Clear and Bit Field Insert. 10.16.1.1 Syntax BFC{cond} Rd, #lsb, #width BFI{cond} Rd, Rn, #lsb, #width where: cond Rd Rn lsb width 10.16.1.2 Operation BFC clears a bitfield in a register. It clears width ...

Page 127

SBFX and UBFX Signed Bit Field Extract and Unsigned Bit Field Extract. 10.16.2.1 Syntax SBFX{cond} Rd, Rn, #lsb, #width UBFX{cond} Rd, Rn, #lsb, #width where: cond Rd Rn lsb width 10.16.2.2 Operation SBFX extracts a bitfield from one register, ...

Page 128

SXT and UXT Sign extend and Zero extend. 10.16.3.1 Syntax SXTextend{cond} {Rd ROR #n} UXTextend{cond} {Rd ROR #n} where: extend B H cond Rd Rm ROR #n ROR #8 Value from Rm is rotated right ...

Page 129

Branch and control instructions Table 10-23 Table 10-23. Branch and control instructions Mnemonic B BL BLX BX CBNZ CBZ IT TBB TBH 11011A–ATARM–04-Oct-10 shows the branch and control instructions: Brief description Branch Branch with Link Branch indirect with Link ...

Page 130

B, BL, BX, and BLX Branch instructions. 10.17.1.1 Syntax B{cond} label BL{cond} label BX{cond} Rm BLX{cond} Rm where BLX cond label but the address to branch to is created by changing bit[0] to ...

Page 131

PC in the BLX instruction • for BX and BLX, bit[ must be 1 for correct execution but a branch occurs to the target address created by changing bit[ • when any ...

Page 132

CBZ and CBNZ Compare and Branch on Zero, Compare and Branch on Non-Zero. 10.17.2.1 Syntax CBZ Rn, label CBNZ Rn, label where: Rn label 10.17.2.2 Operation Use the CBZ or CBNZ instructions to avoid changing the condition code flags ...

Page 133

IT If-Then condition instruction. 10.17.3.1 Syntax IT{x{y{z}}} cond where cond The condition switch for the second, third and fourth instruction in the IT block can be either possible to use AL (the ...

Page 134

PC must either be outside an IT block or must be the last instruction inside the IT block. These are: – ADD PC, PC, Rm – MOV PC, Rm – B, ...

Page 135

TBB and TBH Table Branch Byte and Table Branch Halfword. 10.17.4.1 Syntax TBB [Rn, Rm] TBH [Rn, Rm, LSL #1] where: Rn then the address of the table is the address of the byte immediately following the TBB or ...

Page 136

Examples ADR.W R0, BranchTable_Byte TBB [R0, R1] Case1 ; an instruction sequence follows Case2 ; an instruction sequence follows Case3 ; an instruction sequence follows BranchTable_Byte DCB 0 DCB ((Case2-Case1)/2) DCB ((Case3-Case1)/2) TBH [PC, R1, LSL #1] BranchTable_H DCI ...

Page 137

Miscellaneous instructions Table 10-25 Table 10-25. Miscellaneous instructions Mnemonic BKPT CPSID CPSIE DMB DSB ISB MRS MSR NOP SEV SVC WFE WFI 11011A–ATARM–04-Oct-10 shows the remaining Cortex-M3 instructions: Brief description Breakpoint Change Processor State, Disable Interrupts Change Processor State, ...

Page 138

BKPT Breakpoint. 10.18.1.1 Syntax BKPT #imm where: imm 10.18.1.2 Operation The BKPT instruction causes the processor to enter Debug state. Debug tools can use this to investigate system state when the instruction at a particular address is reached. imm ...

Page 139

CPS Change Processor State. 10.18.2.1 Syntax CPSeffect iflags where: effect IE ID iflags i f 10.18.2.2 Operation CPS changes the PRIMASK and FAULTMASK special register values. See registers” on page 49 10.18.2.3 Restrictions The restrictions are: • use CPS ...

Page 140

DMB Data Memory Barrier. 10.18.3.1 Syntax DMB{cond} where: cond 10.18.3.2 Operation DMB acts as a data memory barrier. It ensures that all explicit memory accesses that appear, in program order, before the DMB instruction are completed before any explicit ...

Page 141

DSB Data Synchronization Barrier. 10.18.4.1 Syntax DSB{cond} where: cond 10.18.4.2 Operation DSB acts as a special data synchronization memory barrier. Instructions that come after the DSB, in program order, do not execute until the DSB instruction completes. The DSB ...

Page 142

ISB Instruction Synchronization Barrier. 10.18.5.1 Syntax ISB{cond} where: cond 10.18.5.2 Operation ISB acts as an instruction synchronization barrier. It flushes the pipeline of the processor, so that all instructions following the ISB are fetched from memory again, after the ...

Page 143

MRS Move the contents of a special register to a general-purpose register. 10.18.6.1 Syntax MRS{cond} Rd, spec_reg where: cond Rd spec_reg PRIMASK, BASEPRI, BASEPRI_MAX, FAULTMASK, or CONTROL. 10.18.6.2 Operation Use MRS in combination with MSR as part of a ...

Page 144

MSR Move the contents of a general-purpose register into the specified special register. 10.18.7.1 Syntax MSR{cond} spec_reg, Rn where: cond Rn spec_reg PRIMASK, BASEPRI, BASEPRI_MAX, FAULTMASK, or CONTROL. 10.18.7.2 Operation The register access operation in MSR depends on the ...

Page 145

NOP No Operation. 10.18.8.1 Syntax NOP{cond} where: cond 10.18.8.2 Operation NOP does nothing. NOP is not necessarily a time-consuming NOP. The processor might remove it from the pipeline before it reaches the execution stage. Use NOP for padding, for ...

Page 146

SEV Send Event. 10.18.9.1 Syntax SEV{cond} where: cond 10.18.9.2 Operation SEV is a hint instruction that causes an event to be signaled to all processors within a multipro- cessor system. It also sets the local event register to 1, ...

Page 147

SVC Supervisor Call. 10.18.10.1 Syntax SVC{cond} #imm where: cond imm 10.18.10.2 Operation The SVC instruction causes the SVC exception. imm is ignored by the processor. If required, it can be retrieved by the exception handler to determine what service ...

Page 148

WFE Wait For Event. 10.18.11.1 Syntax WFE{cond} where: cond 10.18.11.2 Operation WFE is a hint instruction. If the event register is 0, WFE suspends execution until one of the following events occurs: • an exception, unless masked by the ...

Page 149

WFI Wait for Interrupt. 10.18.12.1 Syntax WFI{cond} where: cond 10.18.12.2 Operation WFI is a hint instruction that suspends execution until one of the following events occurs: • an exception • a Debug Entry request, regardless of whether Debug is ...

Page 150

About the Cortex-M3 The address map of the Private peripheral bus (PPB) is: Table 10-26. Core peripheral register regions Address 0xE000E008- 0xE000E00F 0xE000E010- 0xE000E01F 0xE000E100- 0xE000E4EF 0xE000ED00- 0xE000ED3F 0xE000ED90- 0xE000ED93 0xE000EF00- 0xE000EF03 1. In register descriptions: • the register ...

Page 151

Nested Vectored Interrupt Controller This section describes the Nested Vectored Interrupt Controller (NVIC) and the registers it uses. The NVIC supports: • interrupts. • A programmable priority level of 0-15 for each interrupt. A higher level ...

Page 152

Interrupt Priority Registers map to an array of 4-bit integers, so that the array IP[0] to IP[32] corresponds to the registers IPR0-IPR8, and the array entry IP[n] holds the interrupt priority for interrupt n. ...

Page 153

Interrupt Set-enable Registers The ISER0 register enables interrupts, and show which interrupts are enabled. See: • the register summary in • Table 10-28 on page 152 The bit assignments are • ...

Page 154

Interrupt Clear-enable Registers The ICER0 register disables interrupts, and shows which interrupts are enabled. See: • the register summary in • Table 10-28 on page 152 The bit assignments are • ...

Page 155

Interrupt Set-pending Registers The ISPR0 register forces interrupts into the pending state, and shows which interrupts are pending. See: • the register summary in • Table 10-28 on page 152 The bit assignments are ...

Page 156

Interrupt Clear-pending Registers The ICPR0 register removes the pending state from interrupts, and show which interrupts are pending. See: • the register summary in • Table 10-28 on page 152 The bit assignments are ...

Page 157

Interrupt Active Bit Registers The IABR0 register indicates which interrupts are active. See: • the register summary in • Table 10-28 on page 152 The bit assignments are • ACTIVE Interrupt ...

Page 158

Interrupt Priority Registers The IPR0-IPR8 registers provide a 4-bit priority field for each interrupt (See the “Peripheral Iden- tifiers” section of the datasheet for more details). These registers are byte-accessible. See the register summary in fields, that map up ...

Page 159

IPR2 10.20.7.5 IPR1 10.20.7.6 IPR0 • Priority, byte offset 3 • Priority, byte offset 2 ...

Page 160

Find the IPR number and byte offset for interrupt N as follows: • the corresponding IPR number given DIV 4 • the byte offset of the required Priority field in this register is N ...

Page 161

Software Trigger Interrupt Register Write to the STIR to generate a Software Generated Interrupt (SGI). See the register summary in Table 10-27 on page 151 When the USERSETMPEND bit in the SCR is set to 1, unprivileged software can ...

Page 162

Level-sensitive interrupts The processor supports level-sensitive interrupts. A level-sensitive interrupt is held asserted until the peripheral deasserts the interrupt signal. Typ- ically this happens because the ISR accesses the peripheral, causing it to clear the interrupt request. When the ...

Page 163

NVIC design hints and tips Ensure software uses correctly aligned register accesses. The processor does not support unaligned accesses to NVIC registers. See the individual register descriptions for the supported access sizes. A interrupt can enter pending state even ...

Page 164

System control block The System control block (SCB) provides system implementation information, and system con- trol. This includes configuration, control, and reporting of the system exceptions. The system control block registers are: Table 10-30. Summary of the system control ...

Page 165

Auxiliary Control Register The ACTLR provides disable bits for the following processor functions: • IT folding • write buffer use for accesses to the default memory map • interruption of multi-cycle instructions. See the register summary in ments are: ...

Page 166

CPUID Base Register The CPUID register contains the processor part number, version, and implementation informa- tion. See the register summary in are Variant PartNo • Implementer Implementer code: 0x41 = ARM ...

Page 167

Interrupt Control and State Register The ICSR: • provides: – set-pending and clear-pending bits for the PendSV and SysTick exceptions • indicates: – the exception number of the exception being processed – whether there are preempted active exceptions – ...

Page 168

PENDSTSET RW SysTick exception set-pending bit. Write effect 1 = changes SysTick exception state to pending. Read SysTick exception is not pending 1 = SysTick exception is pending. • PENDSTCLR WO SysTick exception clear-pending ...

Page 169

RETTOBASE RO Indicates whether there are preempted active exceptions there are preempted active exceptions to execute 1 = there are no active exceptions, or the currently-executing exception is the only active exception. • VECTACTIVE RO Contains the ...

Page 170

Vector Table Offset Register The VTOR indicates the offset of the vector table base address from memory address 0x00000000. See the register summary in The bit assignments are Reserved TBLOFF • ...

Page 171

Application Interrupt and Reset Control Register The AIRCR provides priority grouping control for the exception model, endian status for data accesses, and reset control of the system. See the register summary in 164 and To write to this register, ...

Page 172

VECTCLRACTIVE WO Reserved for Debug use. This bit reads as 0. When writing to the register you must write 0 to this bit, otherwise behavior is Unpredictable. • VECTRESET WO Reserved for Debug use. This bit reads as 0. ...

Page 173

System Control Register The SCR controls features of entry to and exit from low power state. See the register summary in Table 10-30 on page 164 Reserved • SEVONPEND Send Event ...

Page 174

Configuration and Control Register The CCR controls entry to Thread mode and enables: • the handlers for hard fault and faults escalated by FAULTMASK to ignore bus faults • trapping of divide by zero and unaligned accesses • access ...

Page 175

If this bit is set unaligned access generates a usage fault. Unaligned LDM, STM, LDRD, and STRD instructions always fault irrespective of whether UNALIGN_TRP is set to 1. • ...

Page 176

System Handler Priority Registers The SHPR1-SHPR3 registers set the priority level the exception handlers that have configurable priority. SHPR1-SHPR3 are byte accessible. See the register summary in their attributes. The system fault handlers and the ...

Page 177

System Handler Priority Register 1 The bit assignments are • PRI_7 Reserved • PRI_6 Priority of system handler 6, usage fault • PRI_5 Priority of system handler 5, bus fault • ...

Page 178

System Handler Priority Register 2 The bit assignments are • PRI_11 Priority of system handler 11, SVCall 10.21.9.3 System Handler Priority Register 3 The bit assignments are ...

Page 179

System Handler Control and State Register The SHCSR enables the system handlers, and indicates: • the pending status of the bus fault, memory management fault, and SVC exceptions • the active status of the system handlers. See the register ...

Page 180

MONITORACT Debug monitor active bit, reads Debug monitor is active • SVCALLACT SVC call active bit, reads SVC call is active • USGFAULTACT Usage fault exception active bit, reads exception ...

Page 181

Configurable Fault Status Register The CFSR indicates the cause of a memory management fault, bus fault, or usage fault. See the register summary The following subsections describe the subregisters that ...

Page 182

Memory Management Fault Status Register The flags in the MMFSR indicate the cause of memory access faults. The bit assignments are MMARVALID Reserved • MMARVALID Memory Management Fault Address Register (MMAR) valid flag value in ...

Page 183

Bus Fault Status Register The flags in the BFSR indicate the cause of a bus access fault. The bit assignments are BFRVALID Reserved • BFARVALID Bus Fault Address Register (BFAR) valid flag value in BFAR ...

Page 184

PRECISERR Precise data bus error precise data bus error data bus error has occurred, and the PC value stacked for the exception return points to the instruction that caused the fault. When the ...

Page 185

Usage Fault Status Register The UFSR indicates the cause of a usage fault. The bit assignments are Reserved • DIVBYZERO Divide by zero usage fault divide by zero fault, or divide by ...

Page 186

When this bit is set to 1, the PC value stacked for the exception return points to the instruction that attempted the illegal use of the EPSR. This bit is not set undefined instruction uses the ...

Page 187

Hard Fault Status Register The HFSR gives information about events that activate the hard fault handler. See the register summary in This register is read, write to clear. This means that bits in the register read normally, but writing ...

Page 188

Memory Management Fault Address Register The MMFAR contains the address of the location that generated a memory management fault. See the register summary • ADDRESS When the MMARVALID bit of ...

Page 189

Bus Fault Address Register The BFAR contains the address of the location that generated a bus fault. See the register sum- mary • ADDRESS When the BFARVALID bit of the ...

Page 190

System control block design hints and tips Ensure software uses aligned accesses of the correct size to access the system control block registers: • except for the CFSR and SHPR1-SHPR3, it must use aligned word accesses • for the ...

Page 191

System timer, SysTick The processor has a 24-bit system timer, SysTick, that counts down from the reload value to zero, reloads (wraps to) the value in the LOAD register on the next clock edge, then counts down on subsequent ...

Page 192

SysTick Control and Status Register The SysTick CTRL register enables the SysTick features. See the register summary page 191 Reserved • COUNTFLAG Returns 1 if timer counted to ...

Page 193

SysTick Reload Value Register The LOAD register specifies the start value to load into the VAL register. See the register sum- mary • RELOAD Value to load into the VAL ...

Page 194

SysTick Current Value Register The VAL register contains the current value of the SysTick counter. See the register summary in Table 10-33 on page 191 • CURRENT Reads return the current ...

Page 195

SysTick Calibration Value Register The CALIB register indicates the SysTick calibration properties. See the register summary in Table 10-33 on page 191 31 30 NOREF SKEW • NOREF Reads as zero. • SKEW ...

Page 196

Glossary This glossary describes some of the terms used in technical documents from ARM. Abort A mechanism that indicates to a processor that the value associated with a memory access is invalid. An abort can be caused by the ...

Page 197

Debugger A debugging system that includes a program, used to detect, locate, and correct software faults, together with custom hardware that supports software debugging. Direct Memory Access (DMA) An operation that accesses main memory directly, without the processor performing any ...

Page 198

The behavior is not architecturally defined, and does not have to be documented by individual implementations. Used when there are a number of implementation options available and the option chosen does not affect software compatibility. Index register In some load ...

Page 199

Region A partition of memory space. Reserved A field in a control register or instruction format is reserved if the field defined by the implementation, or produces Unpredictable results if the contents of the field are not ...

Page 200

SAM3N 200 11011A–ATARM–04-Oct-10 ...