DS1921L-F5X Dallas Semiconducotr, DS1921L-F5X Datasheet - Page 21

DS1921L-F5X

Manufacturer Part Number

DS1921L-F5X

Description

Thermochron iButton

Manufacturer

Dallas Semiconducotr

Datasheet

1.DS1921L-F5X.pdf

(40 pages)

DS1921L

Copy Scratchpad [55h]

This command is used to copy data from the scratchpad to the writable memory sections. After issuing

the Copy Scratchpad command, the master must provide a 3-byte authorization pattern, which can be ob-

tained by reading the scratchpad for verification. This pattern must exactly match the data contained in

the three address registers (TA1, TA2, E/S, in that order). If the pattern matches, the AA (Authorization

Accepted) flag will be set and the copy will begin. A pattern of alternating 1s and 0s will be transmitted

after the data has been copied until the master issues a reset pulse. While the copy is in progress any at-

tempt to reset the part will be ignored. Copy typically takes 2µs per byte.

The data to be copied is determined by the three address registers. The scratchpad data from the begin-

ning offset through the ending offset will be copied, starting at the target address. Anywhere from 1 to 32

bytes may be copied to memory with this command. The AA flag will remain at logic 1 until it is cleared

by the next Write Scratchpad command.

Read Memory [F0h]

The Read Memory command may be used to read the entire memory. After issuing the command, the

master must provide the 2-byte target address. After the 2 bytes, the master reads data beginning from the

target address and may continue until the end of memory, at which point logic 0s will be read. It is im-

portant to realize that the target address registers will contain the address provided. The ending offset/data

status byte is unaffected.

The hardware of the DS1921L provides a means to accomplish error-free writing to the memory section.

To safeguard data in the 1-Wire environment when reading and to simultaneously speed up data transfers,

it is recommended to packetize data into data packets of the size of one memory page each. Such a packet

would typically store a 16-bit CRC with each page of data to ensure rapid, error-free data transfers that

eliminate having to read a page multiple times to verify whether if the received data is correct. (See

Chapter 7 of the Book of DS19xx iButton Standards or Application Note 114 for the recommended file

structure.)

Read Memory with CRC [A5h]

The Read Memory with CRC command is used to read memory data that cannot be packetized, such as

the register page and the data recorded by the device during a mission. The command works essentially

the same way as the simple Read Memory, except for the 16-bit CRC that the DS1921L generates and

transmits following the last data byte of a memory page.

After having sent the command code of the Read Memory with CRC command, the bus master sends a 2-

byte address (TA1 = T7:T0, TA2 = T15:T8) that indicates a starting byte location. With the subsequent

read data time slots the master receives data from the DS1921L starting at the initial address and

continuing until the end of a 32-byte page is reached. At that point the bus master will send 16 additional

read data time slots and receive the 16-bit CRC. With subsequent read data time slots the master will

receive data starting at the beginning of the next page followed again by the CRC for that page. This

sequence will continue until the bus master resets the device.

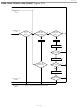

With the initial pass through the Read Memory with CRC flow, the 16-bit CRC value is the result of

shifting the command byte into the cleared CRC generator followed by the 2 address bytes and the

contents of the data memory. Subsequent passes through the Read Memory with CRC flow will generate

a 16-bit CRC that is the result of clearing the CRC generator and then shifting in the contents of the data

memory page. After the 16-bit CRC of the last page is read, the bus master will receive logical 0s from

21 of 40