sm5128a1s Nippon Precision Circuits Inc, (NPC), sm5128a1s Datasheet

sm5128a1s

Related parts for sm5128a1s

sm5128a1s Summary of contents

Page 1

NIPPON PRECISION CIRCUITS INC. OVERVIEW The SM5128A1 transceiver system CMOS IC that incorporates a PLL synthesizer, USA-fre- quency specification code ROM, channel up/down control circuit, LCD driver and channel-change unlock signal generator. All these features in a ...

Page 2

BLOCK DIAGRAM COMA LCD COMB COM COMC LCD S4 DRIVER FIN XIN XOUT PIN DESCRIPTION Number Name 1 COMC LCD common drive signal output LCD segment drive ...

Page 3

Number Name 22 CE PLL start pin. Start when HIGH, and standby mode when LOW. Pull-down resistor built-in Transmit/Receive switch input. Transmit when HIGH, and receive when LOW or open. Pull-down resistor built-in. Emergency channel select input. Channel ...

Page 4

Parameter Symbol FIN and XIN LOW-level input current FIN and XIN HIGH-level input current 2 LOW-level input current 2 HIGH-level input current AI LOW-level input current AI HIGH-level input current Standby current COMA, COMB, COMC LOW-level output voltage COMA, COMB, ...

Page 5

TYPICAL APPLICATION RF 2 VDD LOW BATTERY HIGH POWER LOW POWER 1/3 bias 1/3 duty Display Font DISCONTINUED SM5128A1 PRODUCT 1ST 2ND 2ND 1ST IF MIX IF MIX 10.24MHz MOD VCO VDD 2ND MIX AF ...

Page 6

LCD Segment Diagram S1 COMC LOW BATTERY COMB HIGH POWER COMA LOW POWER Common S1 COMA LOW POWER COMB HIGH POWER COMC LOW BATTERY FUNCTIONAL DESCRIPTION Input Timing The input timing for pins HL, LB, PA, TR and EMG is ...

Page 7

Chattering Elimination Circuit A high-speed chattering elimination circuit is incor- porated in pins UP and DN. The chattering elimina- tion circuit recognizes the input state only after the INPUT SAMPLING CLOCK (Internal) Chatering circuits OUTPUT Note that the input is ...

Page 8

EMG EMG is the emergency channel select pin. The emer- gency channel, channel 9, is selected when EMG is HIGH, and the previously selected channel, deter- EMG 0 to 51.2ms LD PLL DATA CHO UP and DN UP and DN ...

Page 9

the unlock detector pin. The PLL is locked when LD is HIGH, and the PLL is unlocked when LD is LOW. Inputs are LOW (case 1) UP,DN Phase difference (internal) PLL DATA LD External disturbance (case 2) ...

Page 10

Input Pin Priority The device operation for all possible input combina- tions is determined by the active level of the inputs using the following input pin priority. CE > PA > EMG > UP > DN UP,DN EMG LD PLL ...

Page 11

LCD Common/Segment Output Waveforms VDD VSS3 Internal reffrence clock VSS2 VSS1 VDD VSS3 COM1 VSS2 VSS1 VDD VSS3 COM2 VSS2 VSS1 VDD VSS3 COM3 VSS2 VSS1 VDD VSS3 S outoput VSS2 VSS1 Power-ON Initialization When power is applied between VDD ...

Page 12

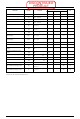

FREQUENCY TABLE USA-speci cation Channel N (T) 1 5393 2 5395 3 5397 4 5401 5 5403 6 5405 7 5407 8 5411 9 5413 10 5415 11 5417 12 5421 13 5423 14 5425 15 5427 16 5431 17 ...

Page 13

DISCONTINUED TR = HIGH Channel N (T) 39 5479 40 5481 SM5128A1 PRODUCT VCO (MHz) N (R) 13.6975 3340 13.7025 3342 NIPPON PRECISION CIRCUITS— LOW (open) VCO (MHz) 16.70 16.71 ...

Page 14

NIPPON PRECISION CIRCUITS INC. reserves the right to make changes to the products contained in this data sheet in order to improve the design or performance and to supply the best possible products. Nippon Precision Circuits Inc. assumes no responsibility ...