adc1225ccd-1 National Semiconductor Corporation, adc1225ccd-1 Datasheet - Page 13

adc1225ccd-1

Manufacturer Part Number

adc1225ccd-1

Description

12-bit Plus Sign Mp Compatible A/d Converters

Manufacturer

National Semiconductor Corporation

Datasheet

1.ADC1225CCD-1.pdf

(18 pages)

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

ADC1225CCD-1

Manufacturer:

AD

Quantity:

74

Functional Description

ADC1205

Case 1 would be the only one that would appy to the

ADC1205 since two RD strobes are necessary to retrieve

the 13 bits of information on the 8 bit data bus Simulta-

neously strobing WR and RD low will enable the most signif-

icant byte on DB0 – DB7 and start a conversion Pulsing

WR RD low before the end of this conversion will enable

the least significant byte of data on the outputs and restart a

conversion

4 0 REFERENCE VOLTAGE

The voltage applied to the reference input of the converter

defines the voltage span of the analog inputs (the difference

between V

put codes and 4096 negative output codes exist The

A-to-D can be used in either ratiometric or absolute refer-

ence applications V

source capable of driving the reference input resistance

(typically 4 kX)

In a ratiometric system the analog input voltage is propor-

tional to the voltage used for the A D reference When this

voltage is the system power supply the V

tied to V

of the system reference as the analog input and A D refer-

ence move together maintaining the same output code for a

given input condition

For absolute accuracy where the analog input varies be-

tween very specific voltage limits the reference pin can be

biased with a time and temperature stable voltage source

In general the magnitude of the reference voltage will re-

quire an initial adjustment to null out full-scale errors

5 0 THE ANALOG INPUTS

5 1 DIFFERENTIAL VOLTAGE INPUTS AND COMMON

MODE REJECTION

The differential inputs of the ADC1225 and ADC1205 actu-

ally reduce the effects of common-mode input noise i e

signals common to both V

most typical) The time interval between sampling the ‘‘

and ‘‘

common-mode voltage during this short time interval may

cause conversion errors For a sinusoidal common-mode

signal the error would be

where f

V

clock frequency In most cases V

cant For a 60 Hz common-mode signal to generate a

LSB error (300 mV) with the converter running at 1 MHz its

peak value would have to be 200mV

5 2 INPUT CURRENT

Due to the sampling nature of the analog inputs short dura-

tion spikes of current enter the ‘‘

input at the leading clock edges during the actual conver-

sion These currents decay rapidly and do not cause errors

as the internal comparator is strobed at the end of a clock

period

5 3 INPUT BYPASS CAPACITORS

Bypass capacitors at the inputs will average the current

spikes mentioned in 5 2 and cause a DC current to flow

PEAK

V

ERROR(MAX)

b

is its peak voltage value and f

‘‘ input is 4 clock periods Therefore a change in the

CM

CC

IN(

is the frequency of the common-mode signal

This technique relaxes the stability requirement

a

)

e

and V

V

REF

PEAK

IN(

b

must be connected to a voltage

IN(

(2

)

q

a

over which 4096 positive out-

f

)

CM

and V

a

ERROR

)

’’ input and exit the ‘‘

f

CLK

4

CLK

IN(

(Continued)

b

will not be signifi-

is the converter’s

)

REF

inputs (60 Hz is

pin can be

a

b

’’

’’

13

through the output resistance of the analog signal source

This charge pumping action is worse for continuous conver-

sions with the V

ous conversions with a 1 MHz clock frequency and the

V

ly 5 mA For this reason bypass capacitors should not be

used at the analog inputs for high resistance sources

(R

If input bypass capacitors are necessary for noise filtering

and high source resistance is desirable to minimize capacitor

size the detrimental effects of the voltage drop across this

input resistance due to the average value of the input cur-

rent can be minimized with a full-scale adjustment while the

given source resistance and input bypass capacitor are both

in place This is effective because the average value of the

input current is a linear function of the differential input volt-

age

5 4 INPUT SOURCE RESISTANCE

Large values of source resistance where an input bypass

capacitor is not used will not cause errors as the input cur-

rents settle out prior to the comparison time If a low pass

filter is required in the system use a low valued series resis-

tor (R

RC active low pass filter For low source resistance applica-

tions (R

the inputs will prevent pickup due to series lead inductance

of a long wire A 100 X series resistor can be used to isolate

this capacitor – both the R and C are placed outside the

feedback loop – from the output of an op amp if used

5 5 NOISE

The leads to the analog inputs should be kept as short as

possible to minimize input noise coupling Both noise and

undesired digital clock coupling to these inputs can cause

errors Input filtering can be used to reduce the effects of

these sources but careful note should be taken of sections

5 3 and 5 4 if this route is taken

6 0 POWER SUPPLIES

Noise spikes on the V

errors as the comparator will respond to this noise Low

inductance tantalum capacitors of 1 mF or greater are rec-

ommended for supply bypassing Separate bypass caps

should be placed close to the DV

unregulated voltage source is available in the system a sep-

arate LM340LAZ-5 0 voltage regulator for the A-to-D’s V

(and other analog circuitry) will greatly reduce digital noise

on the supply line

7 0 ERRORS AND REFERENCE VOLTAGE

7 1 ZERO ADJUST

The zero error of the A D converter relates to the location

of the first riser of the transfer function and can be mea-

sured by grounding the V

magnitude positive voltage to the V

the difference between the actual DC input voltage neces-

sary to just cause an output digital code transition from all

zeroes to 0 0000 0000 0001 and the ideal

LSB

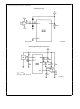

ed as shown in Figure 15 V

V

the digital output code changes from all zeroes to

0 000 0000 0001

IN(

IN(

SOURCE

ADJUSTMENTS

a

b

e

s

)

)

0 61 mV for V

input at 5V the average input current is approximate-

is forced to 0V The potentiometer is adjusted until

100 X) for a passive RC section or add an op amp

SOURCE s

100 X)

IN(

a

100 X) a 0 001 mF bypass capacitor at

)

REF

input voltage at full-scale For continu-

CC

e

supply line can cause conversion

IN(

5 V

IN(

b

DC

)

a

input and applying a small

) Zero error can be adjust-

)

is forced to 0 61 mV and

CC

IN(

a

and AV

)

input Zero error is

LSB value (

CC

pins If an

CC