mc68307ad Freescale Semiconductor, Inc, mc68307ad Datasheet

mc68307ad

Related parts for mc68307ad

mc68307ad Summary of contents

Page 1

MOTOROLA (Parts Not Suitable for New Designs) SEMICONDUCTOR TECHNICAL INFORMATION Technical Summary Integrated Multiple-Bus Processor The MC68307 is an integrated processor combining a static 68EC000 processor with multiple interchip bus interfaces. The MC68307 is designed to provide optimal integration and ...

Page 2

The main features of the MC68307 include: • Static EC000 Core Processor—Identical to MC68EC000 Microprocessor — Full compatibility with MC68000 and MC68EC000 — 24-bit address bus, for 16-Mbyte off-chip address space — 16-bit on-chip data bus for MC68000 bus operations ...

Page 3

The MC68307 is one of a series of components in Motorola's M68300 family. Other members of the family include the MC68302, MC68306, MC68330, MC68331, MC68332, MC68F333, MC68334, MC68340, MC68341, MC68349, and MC68360. ORGANIZATION The M68300 family of integrated processors and ...

Page 4

To improve total system throughput and reduce part count, board size and cost of system implementation, the MC68307 integrates a powerful processor, intelligent peripheral modules, and typical system interface logic. These functions include the SIM07, timers, UART, M-bus interface, and ...

Page 5

Figure 3. Supervisor Programming Model Supplement TRACE MODE SUPERVISOR STATE INTERRUPT MASK EXTEND NEGATIVE CONDITION CODES OVERFLOW MOTOROLA Figure 2. User Programming Model SYSTEM BYTE 15 13 ...

Page 6

Data Types and Addressing Modes Five basic data types are supported: 1.) Bits 2.) Binary coded decimal (BCD) digits (4 bits) 3.) Bytes (8 bits) 4.) Words (16 bits) 5.) Long words (32 bits) In addition, operations on other data ...

Page 7

Register direct addressing Absolute data addressing Program counter relative addressing Register indirect addressing register Immediate data addressing Implied addressing Legend Data Register An = Address Register Xn = Address or Data Register Used as Index Register SR = ...

Page 8

Mnemonic ABCD Add decimal with extend ADD Add ADDA Add address ADDQ Add quick ADDI Add immediate ADDX Add with extend AND Logical AND ANDI AND immediate ANDI to CCR AND immediate to condition codes ANDI to SR AND immediate ...

Page 9

SYSTEM INTEGRATION MODULE The MC68307 system integration module (SIM07) consists of several functions that control the system start-up, initialization, configuration, and the external bus with a minimum of external devices. The SIM07 features include: • System configuration • Oscillator & ...

Page 10

External Bus Interface The external bus interface handles the transfer of information between the internal EC000 core and the memory, peripherals, or other processing elements in the external address space. It consists of a 68000 bus interface and an 8051-compatible ...

Page 11

Low-Power Stop Logic Various options for power-saving are available: turning off unused peripherals, reducing processor clock speed, disabling the processor altogether or a combination of these. A wake-up from power-down can be achieved by causing an interrupt at the interrupt ...

Page 12

MBASE+$040 MBASE+$042 MBASE+$044 MBASE+$046 MBASE+$048 MBASE+$04A MBASE+$04C MBASE+$04E Table 5. SIM07 External Bus Interface Registers Address FC MBASE+$011 S/U MBASE+$013 S/U MBASE+$015 S/U MBASE+$016 S/U MBASE+$018 S/U MBASE+$01A S/U Table 6. SIM07 Interrupt Controller Registers Address FC MBASE+$020 S/U MBASE+$022 ...

Page 13

DUAL TIMER MODULE The MC68307 includes two independent, identical, general-purpose timers. Each general-purpose timer block contains a free-running 16-bit timer which can be used in various modes, to capture the timer value with an external event, to trigger an external ...

Page 14

M-BUS INTERFACE MODULE The M-bus is a two-wire, bidirectional serial bus which provides a simple and efficient means of data exchange between devices fully compatible with the I at 16.67-MHz system clock speed. The maximum communication length and ...

Page 15

UART MODULE The UART module in the MC68307 is based on the MC68681 DUART, which is part of the M68000 family of peripherals which directly interfaces to the MC68000 processor via an asynchronous bus structure. The UART module consists of ...

Page 16

UART Programming Model The programming model for the UART module is listed in Table 10. The FC (function code) column indicates whether a register is restricted to supervisor access (S) or programmable to exist in either supervisor or user space ...

Page 17

EXTERNAL SIGNAL DESCRIPTIONS Figure 5 shows the MC68307 input and output signals in their respective functional groups. Table 11 briefly describes each of the MC68307 signals. CS2B/PA0 CS2C/PA1 CS2D/PA2 MULTIPLEXED TOUT1/PA3 PARALLEL I/O TOUT2/PA4 BR/PA5 BG/PA6 BGACK/PA7 AS UDS LDS ...

Page 18

Mnemonic D15-D0 Data bus A23-A8 Address bus out AD7-AD0/A7-A0 Multiplexed 8051 address/data/Address bus out AS Address strobe UDS Upper data strobe LDS Lower data strobe R/W Read/write DTACK Data acknowledge HALT System halt RESET System reset TRST/RSTIN Power-on reset CS0 ...

Page 19

ELECTRICAL CHARACTERISTICS PRELIMINARY DC ELECTRICAL SPECIFICATIONS Characteristic Input high voltage (except clock) Input low voltage Clock input high voltage Input leakage current @5.25V (all input-only pins) Three-state (off state) input current @2.4V/0.4V Output high voltage (I = rated maximum) OH ...

Page 20

DRIVE TO 2.4 V CLK DRIVE TO 0 2.0 V OUTPUTS (1) CLK VALID OUTPUT n 0.8 V OUTPUTS (2) CLK DRIVE TO 2.4 V INPUTS (3) CLK DRIVE TO 0.5 V INPUTS (4) CLK ALL SIGNALS (5) ...

Page 21

PRELIMINARY AC ELECTRICAL SPECIFICATIONS—CONTROL TIMING (See Figure 7) Num Frequency of operation 1 Cycle time 2,3 Clock pulse width 4,5 Clock rise and fall time 2 NOTE: Timing measurements are referenced to and from a low ...

Page 22

PRELIMINARY AC TIMING SPECIFICATIONS (V = 5.0V 0.5V or 3.3Vdc 0.3V; GND = 0Vdc Num 6 Clock low to address valid 7 Clock high to address, data bus high impedance (maximum) 8 Clock high to address (minimum) a ...

Page 23

PRELIMINARY AC TIMING SPECIFICATIONS (V = 5.0V 0.5V or 3.3Vdc 0.3V; GND = 0Vdc Num 55 R/W asserted to data bus impedance change e 56 HALT/RESET pulse width 57 BGACK negated to AS, CSx, LDS, UDS, R/W driven ...

Page 24

CLK A23–A1 CSx LDS / UDS R/W DTACK D15–D0 BR (NOTE 2) HALT / RESET ASYNCHRONOUS INPUTS (NOTE 1) NOTES: 1. Setup time (#47) for asynchronous inputs (HALT, RESET, BR, BGACK, DTACK) guarantees their recognition at the next ...

Page 25

S0 CLK A23–A1 CSx, AS (NOTE 2) LDS / UDS R/W (NOTE 2) 13 DTACK D15–D0 BR (NOTE 3) HALT / RESET ASYNCHRONOUS INPUTS (NOTE 1) NOTES: 1. Setup time (#47) for asynchronous inputs (HALT, RESET, BR, BGACK, DTACK) guarantees ...

Page 26

CLK Strobes and R/W BR BGACK 35 BG PRELIMINARY 8051 BUS INTERFACE MODULE AC ELECTRICAL SPECIFICATIONS (V = 5.0V 0.5V or 3.3Vdc 0.3V; GND = 0Vdc Symbol Characteristic t Cycle time cyc TLHLL ALE pulse width TAVLL Address ...

Page 27

ALE RD AD7 – AD0 A23–A8 Figure 11. External Dat3a Memory Read Cycle ALE WR TAVLL AD7–AD0 A23–A8 Figure 12. External Data Memory Write Cycle MOTOROLA TLHLL TLLDV TLLWL TRLRH TLLAX TRLDV TAVLL Address TRLAZ TAVWL TAVDV TLHLL TLLWL TWLWH ...

Page 28

PRELIMINARY IEEE 1149.1 ELECTRICAL SPECIFICATIONS (V = 5.0V 0.5V or 3.3Vdc 0.3V; GND = 0Vdc Num Characteristic TCK frequency of operation 1 TCK cycle time 2 TCK clock pulse width measured at 1 TCK rise and ...

Page 29

TCLK TDI TMS TDO TDO TDO Figure 15. Test Access Port Timing Diagram PRELIMINARY TIMER MODULE ELECTRICAL SPECIFICATIONS (V = 5.0V 0.5V or 3.3Vdc 0.3V; GND = 0Vdc Num Characteristic 1 Timer input capture pulse width 2 TINclock ...

Page 30

PRELIMINARY UART ELECTRICAL SPECIFICATIONS (V = 5.0V 0.5V or 3.3Vdc 0.3V; GND = 0Vdc Num Characteristic 1 TxD output valid from TxC low 2 RxD data setup time to RxC high 3 RxD data hold time from RxC ...

Page 31

PRELIMINARY M-BUS INTERFACE INPUT SIGNAL TIMING (V = 5.0V 0.5V or 3.3Vdc 0.3V; GND = 0Vdc Num Characteristic 1 Start condition hold time 2 Clock low period 3 SDA/SCL rise time 4 Data hold time 5 SDA/SCL fall ...

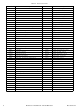

Page 32

The MC68307 is available in a 100-lead QFP package (FG suffix). Figure 20 shows the MC68307 pinout. Figure 21 shows the case drawing for the MC68307 TMS D15 D14 D13 D12 GND D11 D10 ...

Page 33

MC68307FG CASE 842B-01 0. – BASE METAL DETAIL "A" SEATING H PLANE MILLIMETERS INCHES DIM MIN MAX MIN A 19.90 ...

Page 34

The documents listed in the following table contain detailed information on the MC68307. These documents may be obtained from the Literature Distribution Centers at the addresses listed below. Document Title M68300 Integrated Processor Family MC68307 User's Manual M68000 Family Programmer's ...