cop8sgr5vej8xxx National Semiconductor Corporation, cop8sgr5vej8xxx Datasheet - Page 17

cop8sgr5vej8xxx

Manufacturer Part Number

cop8sgr5vej8xxx

Description

8-bit Cmos Rom Based And Otp Microcontrollers With 8k To 32k Memory, Two Comparators And Usart

Manufacturer

National Semiconductor Corporation

Datasheet

1.COP8SGR5VEJ8XXX.pdf

(62 pages)

5.0 Functional Description

The instructions that utilize the stack pointer (SP) always

reference the stack as part of the base segment (Segment

0), regardless of the contents of the S register. The S register

is not changed by these instructions. Consequently, the

stack (used with subroutine linkage and interrupts) is always

located in the base segment. The stack pointer will be initial-

ized to point at data memory location 006F as a result of

reset.

The 128 bytes of RAM contained in the base segment are

split between the lower and upper base segments. The first

112 bytes of RAM are resident from address 0000 to 006F in

the lower base segment, while the remaining 16 bytes of

RAM represent the 16 data memory registers located at

addresses 00F0 to 00FF of the upper base segment. No

RAM is located at the upper sixteen addresses (0070 to

007F) of the lower base segment.

Additional RAM beyond these initial 128 bytes, however, will

always be memory mapped in groups of 128 bytes (or less)

at the data segment address extensions (XX00 to XX7F) of

the lower base segment. The additional 384 bytes of RAM in

this device are memory mapped at address locations 0100

to 017F, 0200 to 027F and 0300 to 037F hex.

Memory address ranges 0200 to 027F and 0300 to 037F are

unavailable on the COP8SGx5 and, if read, will return un-

derfined data.

5.5 ECON (CONFIGURATION) REGISTER

For compatibility with COP8SGx7 devices, mask options are

defined by an ECON Configuration Register which is pro-

grammed at the same time as the program code. Therefore,

the register is programmed at the same time as the program

memory.

(Continued)

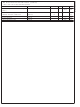

FIGURE 7. RAM Organization

17

The format of the ECON register is as follows:

Bit 7

Bit 6

Bit 5

Bits 4, 3 = 0, 0 External CKI option selected. G7 is avail-

Bit 2

Bit 1

Bit 7

X

Bit 6

POR

= x

= 1

= 0

= 1

= 1

= 0

= 1

= 0, 1 R/C oscillator option selected. G7 is avail-

= 1, 0 Crystal oscillator with on-chip crystal bias

= 1, 1 Crystal oscillator with on-chip crystal bias

SECURITY

Bit 5

This is for factory test. The polarity is “Don’t

Care.”

Power-on reset enabled.

Power-on reset disabled.

Security enabled.

able as a HALT restart and/or general pur-

pose input. CKI is clock input.

able as a HALT restart and/or general pur-

pose input. CKI clock input. Internal R/C

components are supplied for maximum R/C

frequency.

resistor disabled. G7 (CKO) is the clock

generator output to crystal/resonator.

resistor enabled. G7 (CKO) is the clock gen-

erator output to crystal/resonator.

WATCHDOG feature disabled. G1 is a gen-

eral purpose I/O.

WATCHDOG feature enabled. G1 pin is

WATCHDOG output with weak pullup.

Force port I compatibility. Disable port F

outputs and pull-ups. This is intended for

compatibility with existing code and Mask

ROMMed devices only. This bit should be

CKI 2

Bit 4

CKI 1

Bit 3

WATCH

Bit 2

DOG

10131745

F-Port

Bit 1

www.national.com

HALT

Bit 0