am42dl1614dt70it Meet Spansion Inc., am42dl1614dt70it Datasheet - Page 4

am42dl1614dt70it

Manufacturer Part Number

am42dl1614dt70it

Description

16 Mbit X8/x16 Flash And 4 Mbit X16 Static Ram Preliminary

Manufacturer

Meet Spansion Inc.

Datasheet

1.AM42DL1614DT70IT.pdf

(61 pages)

TABLE OF CONTENTS

Product Selector Guide . . . . . . . . . . . . . . . . . . . . . 5

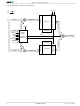

MCP Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . 5

Flash Memory Block Diagram. . . . . . . . . . . . . . . . 6

Connection Diagram . . . . . . . . . . . . . . . . . . . . . . . . 7

Pin Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

Logic Symbol . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

Ordering Information . . . . . . . . . . . . . . . . . . . . . . . 9

Device Bus Operations . . . . . . . . . . . . . . . . . . . . . 10

Common Flash Memory Interface (CFI) . . . . . . . 21

Command Definitions . . . . . . . . . . . . . . . . . . . . . . 24

January 9, 2002

Special Handling Instructions for FBGA Package .................... 7

Word/Byte Configuration ....................................................... 13

Requirements for Reading Array Data ................................... 13

Writing Commands/Command Sequences ............................ 13

Simultaneous Read/Write Operations with Zero Latency ....... 13

Standby Mode ........................................................................ 14

Automatic Sleep Mode ........................................................... 14

RESET#: Hardware Reset Pin ............................................... 14

Output Disable Mode .............................................................. 14

Autoselect Mode ..................................................................... 17

Write Protect (WP#) ................................................................ 17

Temporary Sector/Sector Block Unprotect ............................. 18

SecSi (Secured Silicon) Sector Flash Memory Region .......... 20

Hardware Data Protection ...................................................... 20

Reading Array Data ................................................................ 24

Reset Command ..................................................................... 24

Autoselect Command Sequence ............................................ 24

Enter SecSi Sector/Exit SecSi Sector Command Sequence .. 25

Byte/Word Program Command Sequence ............................. 25

Table 1. Device Bus Operations—Flash Word Mode, CIOf = V

Table 2. Device Bus Operations—Flash Byte Mode, CIOf = V

Accelerated Program Operation .......................................... 13

Autoselect Functions ........................................................... 13

Table 3. Device Bank Division ........................................................14

Table 4. Sector Addresses for Top Boot Sector Devices ............... 15

Table 5. SecSi Sector Addresses for Top Boot Devices ................15

Table 6. Sector Addresses for Bottom Boot Sector Devices ...........16

Table 7. SecSi

Table 8. Top Boot Sector/Sector Block Addresses for Protection/Un-

protection ........................................................................................17

Table 9. Bottom Boot Sector/Sector Block Addresses

for Protection/Unprotection .............................................................17

Figure 1. Temporary Sector Unprotect Operation........................... 18

Figure 2. In-System Sector/Sector Block Protect and Unprotect Algo-

rithms .............................................................................................. 19

Factory Locked: SecSi Sector Programmed and Protected At

the Factory .......................................................................... 20

Customer Lockable: SecSi Sector NOT Programmed or Pro-

tected At the Factory ........................................................... 20

Low V

Write Pulse “Glitch” Protection ............................................ 21

Logical Inhibit ...................................................................... 21

Power-Up Write Inhibit ......................................................... 21

Table 10. CFI Query Identification String........................................ 21

System Interface String................................................................... 22

Table 12. Device Geometry Definition ............................................ 22

Table 13. Primary Vendor-Specific Extended Query ...................... 23

Unlock Bypass Command Sequence .................................. 25

CC

Write Inhibit ........................................................... 20

Addresses for Bottom Boot Devices ..................16

P R E L I M I N A R Y

SS

IH

Am42DL16x4D

... 11

....12

Write Operation Status . . . . . . . . . . . . . . . . . . . . 30

Absolute Maximum Ratings . . . . . . . . . . . . . . . . 34

Operating Ranges . . . . . . . . . . . . . . . . . . . . . . . . . 34

DC Characteristics . . . . . . . . . . . . . . . . . . . . . . . . 35

SRAM DC and Operating Characteristics . . . . . 36

Test Conditions . . . . . . . . . . . . . . . . . . . . . . . . . . 38

Key To Switching Waveforms . . . . . . . . . . . . . . . 38

AC Characteristics . . . . . . . . . . . . . . . . . . . . . . . . 39

Chip Erase Command Sequence ........................................... 26

Sector Erase Command Sequence ........................................ 26

Erase Suspend/Erase Resume Commands ........................... 27

DQ7: Data# Polling ................................................................. 30

RY/BY#: Ready/Busy# ............................................................ 31

DQ6: Toggle Bit I .................................................................... 31

DQ2: Toggle Bit II ................................................................... 32

Reading Toggle Bits DQ6/DQ2 ............................................... 32

DQ5: Exceeded Timing Limits ................................................ 32

DQ3: Sector Erase Timer ....................................................... 32

CMOS Compatible .................................................................. 35

Zero-Power Flash ................................................................. 37

SRAM CE#s Timing ................................................................ 39

Flash Read-Only Operations ................................................. 40

Hardware Reset (RESET#) .................................................... 41

Flash Word/Byte Configuration (CIOf) .................................... 42

Flash Erase and Program Operations .................................... 43

Temporary Sector/Sector Block Unprotect ............................. 48

Figure 3. Program Operation ......................................................... 26

Figure 4. Erase Operation.............................................................. 27

Table 14. Command Definitions (Flash Word Mode) ...................... 28

Table 15. Autoselect Device IDs (Word Mode) .............................. 28

Table 16. Command Definitions (Flash Byte Mode) ....................... 29

Table 17. Autoselect Device IDs (Byte Mode) ............................... 29

Figure 5. Data# Polling Algorithm .................................................. 30

Figure 6. Toggle Bit Algorithm........................................................ 31

Table 18. Write Operation Status ................................................... 33

Industrial (I) Devices ............................................................ 34

V

Figure 9. I

Currents) ........................................................................................ 37

Figure 10. Typical I

Figure 11. Test Setup.................................................................... 38

Table 19. Test Specifications ......................................................... 38

Figure 12. Input Waveforms and Measurement Levels ................. 38

Figure 13. Timing Diagram for Alternating Between

SRAM to Flash ............................................................................... 39

Figure 14. Read Operation Timings ............................................... 40

Figure 15. Reset Timings ............................................................... 41

Figure 16. CIOf Timings for Read Operations................................ 42

Figure 17. CIOf Timings for Write Operations................................ 42

Figure 18. Program Operation Timings.......................................... 44

Figure 19. Accelerated Program Timing Diagram.......................... 44

Figure 20. Chip/Sector Erase Operation Timings .......................... 45

Figure 21. Back-to-back Read/Write Cycle Timings ...................... 46

Figure 22. Data# Polling Timings (During Embedded Algorithms). 46

Figure 23. Toggle Bit Timings (During Embedded Algorithms)...... 47

Figure 24. DQ2 vs. DQ6................................................................. 47

Figure 25. Temporary Sector/Sector Block Unprotect

Timing Diagram.............................................................................. 48

Figure 26. Sector/Sector Block Protect and Unprotect

CC

f/V

CC

s Supply Voltage ................................................... 34

CC1

Current vs. Time (Showing Active and Automatic Sleep

CC1

vs. Frequency ............................................ 37

3