HYB514800BJ-60 SIEMENS [Siemens Semiconductor Group], HYB514800BJ-60 Datasheet

HYB514800BJ-60

Related parts for HYB514800BJ-60

HYB514800BJ-60 Summary of contents

Page 1

... All inputs and outputs TTL-compatible • 1024 refresh cycles / 16 ms • Plastic Packages: P-SOJ-28-2 400 mil width • Package Descriptions P-SOJ-28-2 DRAM (access time 60 ns) P-SOJ-28-2 DRAM (access time 70 ns) P-SOJ-28-2 DRAM (access time 80 ns) 125 01.95 ...

Page 2

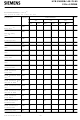

... WRITE OE IO1 - IO8 N. Pin Configuration (top view) Semiconductor Group Address Input Row Address Strobe Column Address Strobe Read/Write Input Output Enable Data Input/Output No Connection Power Supply (+ 5 V) Ground (0 V) P-SOJ-28-2 ( 400 mil width) 126 HYB 514800BJ -60/-70/-80 512k x 8 DRAM ...

Page 3

... Block Diagram Semiconductor Group HYB 514800BJ -60/-70/-80 127 512k x 8 DRAM ...

Page 4

... Semiconductor Group Symbol I( CC1 I CC2 I CC3 I CC4 128 HYB 514800BJ -60/-70/-80 512k x 8 DRAM Limit Values Unit Test Condition min. max. 1) 2.4 6 – 1.0 0 2.4 – – 0 – – – ...

Page 5

... Average supply current during CC CAS before RAS refresh mode -60 version -70 version -80 version Semiconductor Group Symbol min. I – CC5 I CC6 – – – 129 HYB 514800BJ -60/-70/-80 512k x 8 DRAM Limit Values Unit Test Condition max 110 100 90 ...

Page 6

... HYB 514800BJ -60/-70/-80 512k x 8 DRAM -80 max. min. max. – 150 – – 205 – – 50 – – 105 – 70 – – – – ...

Page 7

... HYB 514800BJ -60/-70/-80 512k x 8 DRAM -70 -80 max. min. max – 10 – – 10 – – 0 – – 10 – – 0 – – ...

Page 8

... HYB 514800BJ -60/-70/-80 512k x 8 DRAM -70 -80 max. min. max. – 15 – 16 – 16 – 0 – – 50 – – 110 – – 70 – – 5 – – 15 – ...

Page 9

... MHz Symbol 133 HYB 514800BJ -60/-70/-80 512k x 8 DRAM -70 -80 max. min. max. – 0 – – 20 – – 20 – – 20 – Limit Values Unit min. max. – – ...

Page 10

... RAC t RCD t (max.) can be met. RAC t (max.) limit, then access time is controlled by RAD = 5 ns. T 134 HYB 514800BJ -60/-70/-80 512k x 8 DRAM t t > (min.), the cycle is a read- AWD AWD t (max.) is specified as a RCD (max.) limit, then access time is controlled by t (max.) is specified as a ...

Page 11

... RSH RCD t CAS t RAD t RAL t CAH t ASC Column Address t t RAH RCS OEA t DZC t DZO t CAC t CLZ RAC 135 HYB 514800BJ -60/-70/-80 512k x 8 DRAM CRP t ASR Row Address t RCH t RRH t CDD t ODD t OFF t OEZ Valid Data Out Hi Z ...

Page 12

... Write Cycle (Early Write) Semiconductor Group RAS t CSH t t RCD RSH t CAS t RAD t RAL t CAH t ASC Column Address t CWL t RAH t WCS WCH t RWL Valid Data 136 HYB 514800BJ -60/-70/-80 512k x 8 DRAM CRP t ASR . Row Address ...

Page 13

... Semiconductor Group RAS t CSH t t RCD RSH t CAS t RAD t RAL t CAH t ASC Column Address t CWL t RAH OEH t ODD t DZO DZC t OEZ Valid Data t CLZ t OEA Hi-Z 137 HYB 514800BJ -60/-70/-80 512k x 8 DRAM CRP t ASR Row Address RWL t DH Hi-Z . ...

Page 14

... Address t AWD t t RAD CWD t RWD OEA RCS t DZO t DZC t CLZ t CAC Data Out t RAC 138 HYB 514800BJ -60/-70/-80 512k x 8 DRAM RSH t t CAS CRP t ASR Address t CWL t RWL OEH Valid Data in t ODD t OEZ ...

Page 15

... Fast Page Mode Read-Modify-Write Cycle Semiconductor Group HYB 514800BJ -60/-70/-80 139 512k x 8 DRAM ...

Page 16

... DZC DZC t DZO t DZO t ODD t CAC t t CAC OFF t RAC t OEZ t t CLZ CLZ Valid Data Out 140 HYB 514800BJ -60/-70/-80 512k x 8 DRAM RHCP t RSH t CRP t CAS t CAH t t ASR ASC Column Row Address Address t RCH t RCS t t CPA ...

Page 17

... CWL CWL t WCS t WCS t t WCH WCH Valid Valid Data In Data In HI-Z 141 HYB 514800BJ -60/-70/-80 512k x 8 DRAM RSH t CAS t CRP t RAL t t ASR CAH t ASC Column Column Address Address t CWL t RWL t WCS t WCH t WP ...

Page 18

... V IH RAS CAS ASR V IH A0- I/O1-I/O8 OH (Outputs “H” or “L” RAS-Only Refresh Cycle Semiconductor Group t RAS t RAH Row Address HI-Z 142 HYB 514800BJ -60/-70/-80 512k x 8 DRAM CRP t RPC t ASR Row Address ...

Page 19

... WRITE OEZ CDD V I/O1-I/O8 IH (Inputs ODD V I/O1-I/O8 OH (Outputs OFF “H” or “L” CAS-Before-RAS Refresh Cycle Semiconductor Group t RAS t CSR t CHR t WRP t WRH HI-Z 143 HYB 514800BJ -60/-70/-80 512k x 8 DRAM CRP t RPC ...

Page 20

... RAS t RSH t RCD t WRP t ASC t CAH Column Address t RRH OEA t DZC t DZO t CAC t CLZ t RAC Valid Data Out 144 HYB 514800BJ -60/-70/-80 512k x 8 DRAM RAS t t CHR CRP t ASR t WRH t CDD t ODD t OFF t OEZ HI-Z Row Address ...

Page 21

... Hidden Refresh Cycle (Early Write) Semiconductor Group RAS t t RCD RSH t ASC t CAH Column Address t WCS t WCH Valid Data HI-Z 145 HYB 514800BJ -60/-70/-80 512k x 8 DRAM RAS t t CHR CRP t ASR Row Address ...

Page 22

... WCS t WRP t WRH t DS Valid HI WRP t RCS WRH t CAC DZC t DZO t CAC t CLZ HI-Z 146 HYB 514800BJ -60/-70/-80 512k x 8 DRAM RSH t CAS t RAL CAH AA t CAC t OEA t CDD t ODD t OFF t CLZ OEZ Valid Data Out t RWL t CWL t WCH t ...