MT46H64M16LFCK-5 IT:A Micron Technology Inc, MT46H64M16LFCK-5 IT:A Datasheet - Page 6

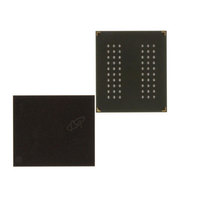

MT46H64M16LFCK-5 IT:A

Manufacturer Part Number

MT46H64M16LFCK-5 IT:A

Description

IC DDR SDRAM 1GBIT 60VFBGA

Manufacturer

Micron Technology Inc

Datasheet

1.MT46H64M16LFCK-5A_TR.pdf

(95 pages)

Specifications of MT46H64M16LFCK-5 IT:A

Format - Memory

RAM

Memory Type

Mobile DDR SDRAM

Memory Size

1G (64M x 16)

Speed

200MHz

Interface

Parallel

Voltage - Supply

1.7 V ~ 1.95 V

Operating Temperature

-40°C ~ 85°C

Package / Case

60-VFBGA

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

List of Figures

Figure 1: 1Gb Mobile LPDDR Part Numbering .................................................................................................. 2

Figure 2: Functional Block Diagram (x16) ......................................................................................................... 9

Figure 3: Functional Block Diagram (x32) ....................................................................................................... 10

Figure 4: 60-Ball VFBGA – 10mm x 11.5mm (Top View) ................................................................................... 11

Figure 5: 90-Ball VFBGA – 10mm x 13mm (Top View) ..................................................................................... 12

Figure 6: 60-Ball VFBGA (10mm x 11.5mm) .................................................................................................... 15

Figure 7: 90-Ball VFBGA (10mm x 13mm) ....................................................................................................... 16

Figure 8: Typical Self Refresh Current vs. Temperature ................................................................................... 23

Figure 9: ACTIVE Command .......................................................................................................................... 34

Figure 10: READ Command ........................................................................................................................... 35

Figure 11: WRITE Command ......................................................................................................................... 36

Figure 12: PRECHARGE Command ................................................................................................................ 37

Figure 13: DEEP POWER-DOWN Command .................................................................................................. 38

Figure 14: Simplified State Diagram ............................................................................................................... 44

Figure 15: Initialize and Load Mode Registers ................................................................................................. 46

Figure 16: Alternate Initialization with CKE LOW ............................................................................................ 47

Figure 17: Standard Mode Register Definition ................................................................................................ 48

Figure 18: CAS Latency .................................................................................................................................. 51

Figure 19: Extended Mode Register ................................................................................................................ 52

Figure 20: Status Read Register Timing .......................................................................................................... 54

Figure 21: Status Register Definition .............................................................................................................. 55

Figure 22: READ Burst ................................................................................................................................... 58

Figure 23: Consecutive READ Bursts .............................................................................................................. 59

Figure 24: Nonconsecutive READ Bursts ........................................................................................................ 60

Figure 25: Random Read Accesses ................................................................................................................. 61

Figure 26: Terminating a READ Burst ............................................................................................................. 62

Figure 27: READ-to-WRITE ............................................................................................................................ 63

Figure 28: READ-to-PRECHARGE .................................................................................................................. 64

Figure 29: Data Output Timing –

Figure 30: Data Output Timing –

Figure 31: Data Output Timing –

Figure 32: Data Input Timing ......................................................................................................................... 69

Figure 33: Write – DM Operation ................................................................................................................... 70

Figure 34: WRITE Burst ................................................................................................................................. 71

Figure 35: Consecutive WRITE-to-WRITE ....................................................................................................... 72

Figure 36: Nonconsecutive WRITE-to-WRITE ................................................................................................. 72

Figure 37: Random WRITE Cycles .................................................................................................................. 73

Figure 38: WRITE-to-READ – Uninterrupting ................................................................................................. 74

Figure 39: WRITE-to-READ – Interrupting ...................................................................................................... 75

Figure 40: WRITE-to-READ – Odd Number of Data, Interrupting .................................................................... 76

Figure 41: WRITE-to-PRECHARGE – Uninterrupting ...................................................................................... 77

Figure 42: WRITE-to-PRECHARGE – Interrupting ........................................................................................... 78

Figure 43: WRITE-to-PRECHARGE – Odd Number of Data, Interrupting ......................................................... 79

Figure 44: Bank Read – With Auto Precharge .................................................................................................. 82

Figure 45: Bank Read – Without Auto Precharge ............................................................................................. 83

Figure 46: Bank Write – With Auto Precharge .................................................................................................. 84

Figure 47: Bank Write – Without Auto Precharge ............................................................................................. 85

Figure 48: Auto Refresh Mode ........................................................................................................................ 86

Figure 49: Self Refresh Mode ......................................................................................................................... 88

Figure 50: Power-down Entry (in Active or Precharge Mode) ........................................................................... 89

PDF: 09005aef82ce3074

1gb_ddr_mobile_sdram_t48m.pdf - Rev. K 07/09 EN

t

t

t

DQSQ,

DQSQ,

AC and

t

t

t

QH, and Data Valid Window (x16) ................................................... 65

QH, and Data Valid Window (x32) ................................................... 66

DQSCK .......................................................................................... 67

6

1Gb: x16, x32 Mobile LPDDR SDRAM

Micron Technology, Inc. reserves the right to change products or specifications without notice.

©2007 Micron Technology, Inc. All rights reserved.