ATMEGA164P-20MU Atmel, ATMEGA164P-20MU Datasheet - Page 312

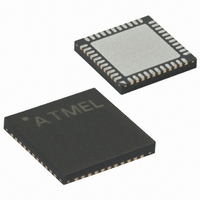

ATMEGA164P-20MU

Manufacturer Part Number

ATMEGA164P-20MU

Description

IC MCU AVR 16K FLASH 44-QFN

Manufacturer

Atmel

Series

AVR® ATmegar

Specifications of ATMEGA164P-20MU

Core Processor

AVR

Core Size

8-Bit

Speed

20MHz

Connectivity

I²C, SPI, UART/USART

Peripherals

Brown-out Detect/Reset, POR, PWM, WDT

Number Of I /o

32

Program Memory Size

16KB (8K x 16)

Program Memory Type

FLASH

Eeprom Size

512 x 8

Ram Size

1K x 8

Voltage - Supply (vcc/vdd)

2.7 V ~ 5.5 V

Data Converters

A/D 8x10b

Oscillator Type

Internal

Operating Temperature

-40°C ~ 85°C

Package / Case

44-VQFN Exposed Pad

Processor Series

ATMEGA16x

Core

AVR8

Data Bus Width

8 bit

Data Ram Size

1 KB

Interface Type

2-Wire/JTAG/SPI/USART

Maximum Clock Frequency

20 MHz

Number Of Programmable I/os

32

Number Of Timers

3

Maximum Operating Temperature

+ 85 C

Mounting Style

SMD/SMT

3rd Party Development Tools

EWAVR, EWAVR-BL

Development Tools By Supplier

ATAVRDRAGON, ATSTK500, ATSTK600, ATAVRISP2, ATAVRONEKIT

Minimum Operating Temperature

- 40 C

On-chip Adc

8-ch x 10-bit

Package

44MLF

Device Core

AVR

Family Name

ATmega

Maximum Speed

20 MHz

Operating Supply Voltage

3.3|5 V

For Use With

ATSTK600-TQFP44 - STK600 SOCKET/ADAPTER 44-TQFPATSTK600 - DEV KIT FOR AVR/AVR32770-1007 - ISP 4PORT ATMEL AVR MCU SPI/JTAGATAVRISP2 - PROGRAMMER AVR IN SYSTEM

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Part Number:

ATMEGA164P-20MU

Manufacturer:

ATMEL/爱特梅尔

Quantity:

20 000

- Current page: 312 of 439

- Download datasheet (10Mb)

24.9.1

24.10 Programming via the JTAG Interface

24.10.1

8011O–AVR–07/10

Serial Programming Characteristics

Programming Specific JTAG Instructions

For characteristics of the Serial Programming module see “SPI Timing Characteristics” on page

332.

Figure 24-12. Serial Programming Waveforms

Programming through the JTAG interface requires control of the four JTAG specific pins: TCK,

TMS, TDI, and TDO. Control of the reset and clock pins is not required.

To be able to use the JTAG interface, the JTAGEN Fuse must be programmed. The device is

default shipped with the fuse programmed. In addition, the JTD bit in MCUCR must be cleared.

Alternatively, if the JTD bit is set, the external reset can be forced low. Then, the JTD bit will be

cleared after two chip clocks, and the JTAG pins are available for programming. This provides a

means of using the JTAG pins as normal port pins in Running mode while still allowing In-Sys-

tem Programming via the JTAG interface. Note that this technique can not be used when using

the JTAG pins for Boundary-scan or On-chip Debug. In these cases the JTAG pins must be ded-

icated for this purpose.

During programming the clock frequency of the TCK Input must be less than the maximum fre-

quency of the chip. The System Clock Prescaler can not be used to divide the TCK Clock Input

into a sufficiently low frequency.

As a definition in this datasheet, the LSB is shifted in and out first of all Shift Registers.

The Instruction Register is 4-bit wide, supporting up to 16 instructions. The JTAG instructions

useful for programming are listed below.

The OPCODE for each instruction is shown behind the instruction name in hex format. The text

describes which Data Register is selected as path between TDI and TDO for each instruction.

The Run-Test/Idle state of the TAP controller is used to generate internal clocks. It can also be

used as an idle state between JTAG sequences. The state machine sequence for changing the

instruction word is shown in

SERIAL DATA OUTPUT

SERIAL CLOCK INPUT

SERIAL DATA INPUT

SAMPLE

(MOSI)

(MISO)

(SCK)

Figure 24-13 on page

MSB

MSB

ATmega164P/324P/644P

313.

LSB

LSB

312

Related parts for ATMEGA164P-20MU

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

8-bit Microcontroller With 16/32/64k Bytes In-system Programmable Flash - Atmel Corporation

Manufacturer:

ATMEL Corporation

Datasheet:

Part Number:

Description:

8-bit Microcontroller with 16/32/64K Bytes In-System Programmable Flash

Manufacturer:

ATMEL [ATMEL Corporation]

Datasheet:

Part Number:

Description:

Manufacturer:

Atmel Corporation

Datasheet:

Part Number:

Description:

IC AVR MCU 16K 16MHZ 5V 44TQFP

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

IC AVR MCU 16K 16MHZ 5V 44-QFN

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

IC AVR MCU 16K 16MHZ 5V 40DIP

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

MCU AVR 16K FLASH 16MHZ 44-QFN

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

IC AVR MCU 16K 16MHZ COM 40-DIP

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

IC AVR MCU 16K 16MHZ COM 44-QFN

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

IC AVR MCU 16K 16MHZ IND 40-DIP

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

IC AVR MCU 16K 16MHZ IND 44-QFN

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

IC AVR MCU 16K 16MHZ IND 44-TQFP

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

IC MCU 8BIT 16KB FLASH 44TQFP

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

MCU AVR 16K FLASH 16MHZ 44-TQFP

Manufacturer:

Atmel

Datasheet: