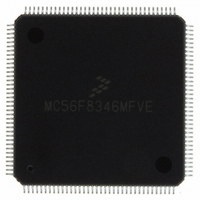

MC56F8346MFVE Freescale Semiconductor, MC56F8346MFVE Datasheet - Page 108

MC56F8346MFVE

Manufacturer Part Number

MC56F8346MFVE

Description

IC DSP 16BIT 60MHZ 144-LQFP

Manufacturer

Freescale Semiconductor

Series

56F8xxxr

Datasheet

1.MC56F8346VFVE.pdf

(178 pages)

Specifications of MC56F8346MFVE

Core Processor

56800

Core Size

16-Bit

Speed

60MHz

Connectivity

CAN, EBI/EMI, SCI, SPI

Peripherals

POR, PWM, Temp Sensor, WDT

Number Of I /o

62

Program Memory Size

136KB (68K x 16)

Program Memory Type

FLASH

Ram Size

6K x 16

Voltage - Supply (vcc/vdd)

2.25 V ~ 3.6 V

Data Converters

A/D 16x12b

Oscillator Type

External

Operating Temperature

-40°C ~ 125°C

Package / Case

144-LQFP

Data Bus Width

16 bit

Processor Series

MC56F83xx

Core

56800E

Numeric And Arithmetic Format

Fixed-Point

Device Million Instructions Per Second

60 MIPs

Maximum Clock Frequency

60 MHz

Number Of Programmable I/os

62

Data Ram Size

4 KB

Operating Supply Voltage

3.6 V

Maximum Operating Temperature

+ 125 C

Mounting Style

SMD/SMT

Interface Type

SCI, SPI, CAN

Minimum Operating Temperature

- 40 C

For Use With

MC56F8367EVME - EVAL BOARD FOR MC56F83X

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Eeprom Size

-

Lead Free Status / Rohs Status

Lead free / RoHS Compliant

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

MC56F8346MFVE

Manufacturer:

Freescale

Quantity:

42

Company:

Part Number:

MC56F8346MFVE

Manufacturer:

Freescale Semiconductor

Quantity:

10 000

Part Number:

MC56F8346MFVE

Manufacturer:

FREESCALE

Quantity:

20 000

5.6.30.2

These read-only bits reflect the state of the new interrupt priority level bits being presented to the 56800E

core at the time the last IRQ was taken. This field is only updated when the 56800E core jumps to a new

interrupt service routine.

Note:

5.6.30.3

This read-only field shows the vector number (VAB[7:1]) used at the time the last IRQ was taken. This

field is only updated when the 56800E core jumps to a new interrupt service routine.

Note:

5.6.30.4

This bit allows all interrupts to be disabled.

5.6.30.5

This bit field is reserved or not implemented. It is read as 1 and cannot be modified by writing.

5.6.30.6

This read-only bit reflects the state of the external IRQB pin.

5.6.30.7

This read-only bit reflects the state of the external IRQA pin.

5.6.30.8

This bit controls whether the external IRQB interrupt is edge- or level-sensitive. During Stop and Wait

modes, it is automatically level-sensitive.

108

•

•

•

•

•

•

•

•

•

1 = An interrupt is being sent to the 56800E core

00 = Required nested exception priority levels are 0, 1, 2, or 3

01 = Required nested exception priority levels are 1, 2, or 3

10 = Required nested exception priority levels are 2 or 3

11 = Required nested exception priority level is 3

0 = Normal operation (default)

1 = All interrupts disabled

0 = IRQB interrupt is a low-level sensitive (default)

1 = IRQB interrupt is falling-edge sensitive.

Nested interrupts may cause this field to be updated before the original interrupt service routine can

read it.

Nested interrupts may cause this field to be updated before the original interrupt service routine can

read it.

Interrupt Priority Level (IPIC)—Bits 14–13

Vector Number - Vector Address Bus (VAB)—Bits 12–6

Interrupt Disable (INT_DIS)—Bit 5

Reserved—Bit 4

IRQB State Pin (IRQB STATE)—Bit 3

IRQA State Pin (IRQA STATE)—Bit 2

IRQB Edge Pin (IRQB Edg)—Bit 1

56F8346 Technical Data, Rev. 15

Freescale Semiconductor

Preliminary