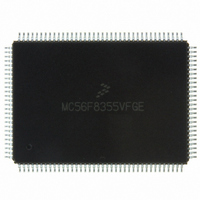

MC56F8355VFGE Freescale Semiconductor, MC56F8355VFGE Datasheet - Page 124

MC56F8355VFGE

Manufacturer Part Number

MC56F8355VFGE

Description

IC DSP 16BIT 60MHZ 128-LQFP

Manufacturer

Freescale Semiconductor

Series

56F8xxxr

Datasheet

1.MC56F8355VFGE.pdf

(172 pages)

Specifications of MC56F8355VFGE

Core Processor

56800

Core Size

16-Bit

Speed

60MHz

Connectivity

CAN, EBI/EMI, SCI, SPI

Peripherals

POR, PWM, Temp Sensor, WDT

Number Of I /o

49

Program Memory Size

264KB (132K x 16)

Program Memory Type

FLASH

Ram Size

10K x 16

Voltage - Supply (vcc/vdd)

2.25 V ~ 3.6 V

Data Converters

A/D 16x12b

Oscillator Type

External

Operating Temperature

-40°C ~ 105°C

Package / Case

128-LQFP

Data Bus Width

16 bit

Processor Series

MC56F83xx

Core

56800E

Numeric And Arithmetic Format

Fixed-Point

Device Million Instructions Per Second

60 MIPs

Maximum Clock Frequency

60 MHz

Number Of Programmable I/os

49

Data Ram Size

20 KB

Maximum Operating Temperature

+ 105 C

Mounting Style

SMD/SMT

Interface Type

SCI, SPI, CAN

Minimum Operating Temperature

- 40 C

For Use With

MC56F8367EVME - EVAL BOARD FOR MC56F83X

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Eeprom Size

-

Lead Free Status / Rohs Status

Lead free / RoHS Compliant

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

MC56F8355VFGE

Manufacturer:

Freescale

Quantity:

562

Company:

Part Number:

MC56F8355VFGE

Manufacturer:

Freescale Semiconductor

Quantity:

10 000

Part Number:

MC56F8355VFGE

Manufacturer:

FREESCALE

Quantity:

20 000

The value of the JTAG FM_CLKDIV[6:0] will replace the value of the FM register FMCLKD that divides

down the system clock for timed events, as illustrated in

PRDIV8 bit, and FM_CLKDIV[5:0] will map to the DIV[5:0] bits. The combination of PRDIV8 and DIV

must divide the FM input clock down to a frequency of 150kHz-200kHz. The “Writing the FMCLKD

Register” section in the Flash Memory chapter of the 56F8300 Peripheral User Manual gives specific

equations for calculating the correct values.

Two examples of FM_CLKDIV calculations follow.

EXAMPLE 1: If the system clock is the 8MHz crystal frequency because the PLL has not been set up,

the input clock will be below 12.8MHz, so PRDIV8 = FM_CLKDIV[6] = 0. Using the following equation

yields a DIV value of 19 for a clock of 200kHz, and a DIV value of 20 for a clock of 190kHz. This

translates into an FM_CLKDIV[6:0] value of $13 or $14, respectively.

EXAMPLE 2: In this example, the system clock has been set up with a value of 32MHz, making the FM

124

JTAG

SYS_CLK

2

Figure 7-1 JTAG to FM Connection for Lockout Recovery

FM_CLKDIV

FM_ERASE

150[kHz]

56F8355 Technical Data, Rev. 17

<

(

FMCLKD

clock

input

SYS_CLK

(DIV + 1)

(2)

7

)

Figure

<

Flash Memory

7

200[kHz]

7-1. FM_CLKDIV[6] will map to the

DIVIDER

7

Freescale Semiconductor

Preliminary