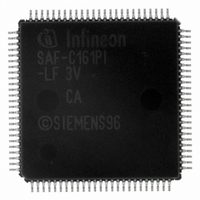

SAF-C161PI-LF 3V CA Infineon Technologies, SAF-C161PI-LF 3V CA Datasheet - Page 51

SAF-C161PI-LF 3V CA

Manufacturer Part Number

SAF-C161PI-LF 3V CA

Description

IC MCU 16BIT ROM/LESS TQFP-100-1

Manufacturer

Infineon Technologies

Series

C16xxr

Datasheet

1.SAF-C161PI-LM_CA.pdf

(82 pages)

Specifications of SAF-C161PI-LF 3V CA

Core Processor

C166

Core Size

16-Bit

Speed

20MHz

Connectivity

EBI/EMI, I²C, SPI, UART/USART

Peripherals

POR, PWM, WDT

Number Of I /o

76

Program Memory Type

ROMless

Ram Size

3K x 8

Voltage - Supply (vcc/vdd)

3 V ~ 3.6 V

Data Converters

A/D 4x10b

Oscillator Type

Internal

Operating Temperature

-40°C ~ 85°C

Package / Case

100-LFQFP

Data Bus Width

16 bit

Data Ram Size

3 KB

Interface Type

ASC, I2C, SSC

Maximum Clock Frequency

25 MHz

Number Of Programmable I/os

76

Number Of Timers

5

Maximum Operating Temperature

+ 85 C

Mounting Style

SMD/SMT

Minimum Operating Temperature

- 40 C

On-chip Adc

10 bit, 4 Channel

Packages

PG-TQFP-100

Max Clock Frequency

20.0 MHz

Sram (incl. Cache)

3.0 KByte

A / D Input Lines (incl. Fadc)

4

Program Memory

0.0 KByte

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Eeprom Size

-

Program Memory Size

-

Lead Free Status / Rohs Status

Details

Other names

F161PILF3VCAXT

SAF-C161PI-LF3VCA

SAF-C161PI-LF3VCAINTR

SAF-C161PI-LF3VCATR

SAF-C161PI-LF3VCATR

SAFC161PILF3VCAXT

SP000014361

SAF-C161PI-LF3VCA

SAF-C161PI-LF3VCAINTR

SAF-C161PI-LF3VCATR

SAF-C161PI-LF3VCATR

SAFC161PILF3VCAXT

SP000014361

AC Characteristics

External Clock Drive XTAL1 (Standard Supply Voltage Range)

(Operating Conditions apply)

Parameter

Oscillator period

High time

Low time

Rise time

Fall time

1) The minimum and maximum oscillator periods for PLL operation depend on the selected CPU clock generation

2) The clock input signal must reach the defined levels

3) The minimum high and low time refers to a duty cycle of 50%. The maximum operating frequency (

AC Characteristics

External Clock Drive XTAL1 (Reduced Supply Voltage Range)

(Operating Conditions apply)

Parameter

Oscillator period

High time

Low time

Rise time

Fall time

1) The minimum and maximum oscillator periods for PLL operation depend on the selected CPU clock generation

2) The clock input signal must reach the defined levels

3) The minimum high and low time refers to a duty cycle of 50%. The maximum operating frequency (

Data Sheet

mode. Please see respective table above.

direct drive mode depends on the duty cycle of the clock input signal.

mode. Please see respective table above.

direct drive mode depends on the duty cycle of the clock input signal.

2)

2)

2)

2)

2)

2)

2)

2)

Symbol

Symbol

OSC

1

2

3

4

OSC

1

2

3

4

SR

SR

SR

SR

SR

SR

SR

SR

SR

SR

40

20

20

–

–

50

25

25

–

–

min.

min.

Direct Drive

Direct Drive

3)

3)

3)

3)

1:1

1:1

–

–

–

10

10

–

–

–

10

10

max.

max.

49

IL

IL

and

and

20

6

6

–

–

25

8

8

–

–

min.

min.

Prescaler

Prescaler

IH2

IH2

.

.

2:1

2:1

–

–

–

6

6

–

–

–

6

6

max.

max.

60

10

10

–

–

60

10

10

–

–

min.

min.

1)

1)

PLL

PLL

1:N

1:N

500

–

–

10

10

500

–

–

10

10

max.

max.

1)

1)

&3,

1999-07

Unit

ns

ns

ns

ns

ns

Unit

ns

ns

ns

ns

ns

CPU

CPU

) in

) in