MCIMX515CJM6C Freescale Semiconductor, MCIMX515CJM6C Datasheet - Page 62

MCIMX515CJM6C

Manufacturer Part Number

MCIMX515CJM6C

Description

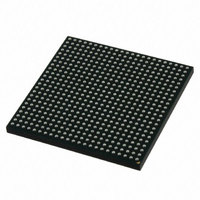

MULTIMEDIA PROC 529-LFBGA

Manufacturer

Freescale Semiconductor

Series

i.MX51r

Datasheets

1.MCIMX512DJM8C.pdf

(200 pages)

2.MCIMX515DJM8C.pdf

(2 pages)

3.MCIMX512CJM6C.pdf

(198 pages)

Specifications of MCIMX515CJM6C

Core Processor

ARM Cortex-A8

Core Size

32-Bit

Speed

600MHz

Connectivity

1-Wire, EBI/EMI, Ethernet, I²C, IrDA, MMC, SPI, SSI, UART/USART, USB OTG

Peripherals

DMA, I²S, LCD, POR, PWM, WDT

Number Of I /o

128

Program Memory Type

ROMless

Ram Size

128K x 8

Voltage - Supply (vcc/vdd)

0.8 V ~ 1.15 V

Oscillator Type

External

Operating Temperature

-20°C ~ 85°C

Package / Case

529-LFBGA

Processor Series

i.MX51

Core

ARM Cortex A8

Data Bus Width

32 bit

Program Memory Size

36 KB

Data Ram Size

128 KB

Interface Type

I2C, SPI, SSI, UART, USB

Maximum Clock Frequency

200 MHz

Number Of Timers

5

Operating Supply Voltage

0.8 V to 1.15 V

Maximum Operating Temperature

+ 95 C

Mounting Style

SMD/SMT

3rd Party Development Tools

MDK-ARM, RL-ARM, ULINK2

Development Tools By Supplier

MCIMX51EVKJ

Minimum Operating Temperature

- 40 C

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Eeprom Size

-

Program Memory Size

-

Data Converters

-

Lead Free Status / Rohs Status

Lead free / RoHS Compliant

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

MCIMX515CJM6C

Manufacturer:

Freescale Semiconductor

Quantity:

10 000

Part Number:

MCIMX515CJM6C

Manufacturer:

FREESCALE

Quantity:

20 000

Company:

Part Number:

MCIMX515CJM6CR2

Manufacturer:

Freescale Semiconductor

Quantity:

10 000

Electrical Characteristics

62

1

2

3

4

5

6

7

8

WE43 Input Data Valid to CSx_B

WE44 CSx_B Invalid to Input Data

WE45 CSx_B Valid to BEy_B Valid

WE46 BEy_B Invalid to CSx_B Invalid

WE47 Dtack Valid to CSx_B Invalid

WE48 CSx_B Invalid to Dtack invalid

Parameters WE4... WE21 value see in the

CS Assertion. This bit field determines when CS signal is asserted during read/write cycles.

CS Negation. This bit field determines when CS signal is negated during read/write cycles.

BE Assertion. This bit field determines when BE signal is asserted during read cycles.

BE Negation. This bit field determines when BE signal is negated during read cycles.

Output maximum delay from internal driving the FFs to chip outputs. The Max. delay between all memory controls (addr,

csx_b, oe_b, we_b, bey_b, and adv_b)

Maximum delay from chip input data to internal FFs. The max. delay between all data input pins.

DTACK maximum delay from chip input data to internal FF.

ID

Invalid

invalid

(Write access)

(Write access)

Table 54. WEIM Asynchronous Timing Parameters Table Relative Chip Select (continued)

Parameter

i.MX51 Applications Processors for Consumer and Industrial Products, Rev. 4

MAXCO + MAXDI

0

WE12 – WE6 + (WBEA – CSA)

WE7 – WE13 + (WBEN – CSN)

MAXCO + MAXDTI

0

Synchronous Measured

Table

Determination by

Parameters

54.

1

MAXCO

MAXCO

6

Min

6

—

—

+ MAXDTI

0

0

+ MAXDI

7

8

–3 + (WBEN – CSN)

3 + (WBEA – CSA)

Freescale Semiconductor

Max

—

—

—

—

Unit

ns

ns

ns

ns

ns

ns