LS-E2-L-BASE-PC-N Lattice, LS-E2-L-BASE-PC-N Datasheet - Page 16

LS-E2-L-BASE-PC-N

Manufacturer Part Number

LS-E2-L-BASE-PC-N

Description

MCU, MPU & DSP Development Tools ispLEVER Base - LS ECP2 50E Std Dev Kit

Manufacturer

Lattice

Datasheet

1.LFE2-50E-L-EV.pdf

(34 pages)

Specifications of LS-E2-L-BASE-PC-N

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Lattice Semiconductor

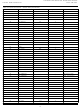

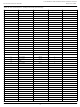

Table 28. PCI Connections - Component Side (Continued)

PCI/PCI-X Jumpers

Table 29. PRSNT1

Table 30. PRSNT2

Table 31. PCIXCAP and M66EN Encoding

Table 32. PCI TDI and TDO

Table 33. PCI Interrupt

Note: PD = pull-down resistor, PU = pull-up resistor, NC = no-connect, TP = test point.

Not installed. If installing header, first cut trace between 2 and 3. If master, also install R51 and C39.

Not installed. If master, also install R62 and C47.

Not installed. If master then cut the trace between 1 and 2.

Not installed. If installing header, first cut trace between 2 and 4.

Location

Location

Location

Location

J23

J13

J19

If master, also install R126 and C111.

J9

PCIXCAP(J24)

J14

93

94

Don’t Care

1 to 2

1 to 2

Open

Open

Position

Position

Position

Position

1 to 2

2 to 3

Open

1 to 2

Open

1 to 2

2 to 4

1 to 3

4 to 6

3 to 5

Open

NC

GND

Signal Name

M66EN(J38)

Master PCI/PCI-X

Target PCI/PCI-X

Target PCI/PCI-X

Master PCI/PCI-X

Target PCI/PCI-X

Target PCI/PCI-X

Master PCI/PCI-X

INT = INTA

INT = INTB

INT = INTC

INT = INTD

Open

2 to 3

Open

2 to 3

1 to 2

LatticeECP2 Pin

33MHz

66MHz

33MHz

66MHz

Master

PCI

16

-

-

Function

Function

Function

Function

Frequency

LatticeECP2 Standard Evaluation Board

133MHz

133MHz

66MHz

66MHz

sysIO Bank

Master

PCI-X

-

-

Default

User’s Guide

X

Notes

Default

Default

Default

Default

X

X

X

X