SAA7105E/V1/G-T NXP Semiconductors, SAA7105E/V1/G-T Datasheet - Page 31

SAA7105E/V1/G-T

Manufacturer Part Number

SAA7105E/V1/G-T

Description

Video ICs PC-DENC

Manufacturer

NXP Semiconductors

Datasheet

1.SAA7105EV1G-T.pdf

(70 pages)

Specifications of SAA7105E/V1/G-T

Adc/dac Resolution

10b

Screening Level

Commercial

Package Type

LBGA

Pin Count

156

Lead Free Status / RoHS Status

Compliant

Other names

SAA7105E/V1/G,518

Philips Semiconductors

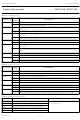

Table 31 Subaddress 29H

Table 32 Subaddresses 2AH to 2CH

Table 33 Subaddress 2DH

2004 Mar 04

SRES

BE

CG

CGEN

VBSEN

CVBSEN1

CVBSEN0

CEN

ENCOFF

CLK2EN

CVBSEN2

DATA BYTE

DATA BYTE

DATA BYTE

Digital video encoder

LEVEL

LEVEL

LEVEL

LOGIC

LOGIC

LOGIC

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

pin TTX_SRES accepts a teletext bit

stream (TTX)

pin TTX_SRES accepts a sync reset input

(SRES)

ending point of burst in clock cycles

LSBs of the respective bytes are encoded immediately after run-in, the MSBs of the

respective bytes have to carry the CRCC bits, in accordance with the definition of copy

generation management system encoding format.

copy generation data output is disabled; default after reset

copy generation data output is enabled

pin GREEN_VBS_CVBS provides a component GREEN signal (CVBSEN1 = 0) or CVBS

signal (CVBSEN1 = 1)

pin GREEN_VBS_CVBS provides a luminance (VBS) signal; default after reset

pin GREEN_VBS_CVBS provides a component GREEN (G) or luminance (VBS) signal;

default after reset

pin GREEN_VBS_CVBS provides a CVBS signal

pin BLUE_CB_CVBS provides a component BLUE (B) or colour difference BLUE (C

pin BLUE_CB_CVBS provides a CVBS signal; default after reset

pin RED_CR_C_CVBS provides a component RED (R) or colour difference RED (C

pin RED_CR_C_CVBS provides a chrominance signal (C) as modulated subcarrier for

S-video; default after reset

encoder is active; default after reset

encoder bypass, DACs are provided with RGB signal after cursor insertion block

pin TTXRQ_XCLKO2 provides a teletext request signal (TTXRQ)

pin TTXRQ_XCLKO2 provides the buffered crystal clock divided by two (13.5 MHz); default

after reset

pin RED_CR_C_CVBS provides a signal according to CEN; default after reset

pin RED_CR_C_CVBS provides a CVBS signal

DESCRIPTION

31

DESCRIPTION

DESCRIPTION

default after reset

a HIGH impulse resets synchronization of the

encoder (first field, first line)

PAL: BE = 29 (1DH); default after reset if

strapping pin FSVGC tied to HIGH

NTSC: BE = 29 (1DH); default after reset if

strapping pin FSVGC tied to LOW

SAA7104E; SAA7105E

REMARKS

Product specification

R

B

) signal

) signal