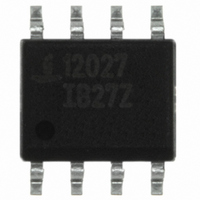

ISL12027IB27Z-T Intersil, ISL12027IB27Z-T Datasheet

ISL12027IB27Z-T

Specifications of ISL12027IB27Z-T

Available stocks

Related parts for ISL12027IB27Z-T

ISL12027IB27Z-T Summary of contents

Page 1

... I C-bus™ trademark of NXP B.V. BlockLock™ trademark of Intersil Corporation or one of its subsidiaries All other trademarks mentioned are the property of their respective owners. ISL12027, ISL12027A FN8232.8 Intersil (and design registered trademark of Intersil Americas Inc. Copyright Intersil Americas Inc. 2005, 2006, 2010. All Rights Reserved ...

Page 2

... This input provides a backup supply voltage to the device. V BAT that the Power Supply. DD Ordering Information PART NUMBER PART V (Notes MARKING ISL12027IB27Z 12027 IB27Z ISL12027IB27AZ 12027 IB27AZ ISL12027IB30AZ 12027 IB30AZ ISL12027IBZ 12027 IBZ ISL12027IBAZ 12027 IBAZ ISL12027IV27Z 2027 I27Z ISL12027IV27AZ 2027 27AZ ISL12027IV30AZ ...

Page 3

Block Diagram X1 32.768kHZ X2 CONTROL SERIAL SCL DECODE INTERFACE LOGIC DECODER SDA 8 RESET 3 ISL12027, ISL12027A OSC COMPENSATION TIMER 1Hz FREQUENCY CALENDAR OSCILLATOR DIVIDER LOGIC STATUS CONTROL/ REGISTERS ALARM REGISTERS (SRAM) (EEPROM) WATCHDOG LOW VOLTAGE TIMER RESET BATTERY ...

Page 4

... Ld SOIC Package (Notes TSSOP Package (Notes Maximum Junction Temperature (Plastic Package +150°C Storage Temperature . . . . . . . . . . . . . . . . . . . . . . . .-65°C to +150°C Pb-free reflow profile . . . . . . . . . . . . . . . . . . . . . . . . . .see link below http://www.intersil.com/pbfree/Pb-FreeReflow.asp = +2.7V to +5.5V 3.3V. Boldface limits apply over the operating temperature range, -40°C to +85°C. DD ...

Page 5

Watchdog Timer/Low Voltage Reset Parameters SYMBOL PARAMETER t V Detect to RESET LOW RPD DD t Power-up Reset Time-Out Delay PURST V Minimum V for Valid RESET RVALID DD Output V ISL12027-4.5A Reset Voltage Level RESET ISL12027 Reset Voltage Level ...

Page 6

Serial Interface (I C) Specifications SYMBOL PARAMETER t START Condition Set-up Time SU:STA t START Condition Hold Time HD:STA t Input Data Set-up Time SU:DAT t Input Data Hold Time HD:DAT t STOP Condition Set-up Time SU:STO t STOP ...

Page 7

Timing Diagrams SCL t SU:STA t HD:STA SDA (INPUT TIMING) SDA (OUTPUT TIMING) SCL 8TH BIT OF LAST BYTE SDA t RSP SCL SDA RESET START Note: All inputs are ignored during the active reset period (t V RESET V ...

Page 8

Typical Performance Curves 4.0 BSW = 3.5 SCL, SDA PULL-UPS = 0V 3.0 2.5 2.0 1.5 SCL, SDA PULL-UPS = V 1.0 0.5 BSW = 0.0 1.8 2.3 2.8 3.3 3.8 V (V) BAT ...

Page 9

Description The ISL12027 device is a Real Time Clock with clock/calendar, two polled alarms with integrated 512x8 EEPROM configured in 16 Byte per page format, oscillator compensation, CPU Supervisor (Power on Reset, Low Voltage Sensing and Watchdog Timer) and battery ...

Page 10

... For example, a >20ppm frequency deviation translates into an accuracy of >1 minute per month. These parameters are available from the crystal manufacturer. Intersil’s RTC family provides on- chip crystal compensation networks to adjust load-capacitance to tune oscillator frequency from -34ppm to +80ppm when using a 12.5pF load crystal. For more detailed information see “ ...

Page 11

MIL = 1), DT (Date 31, MO (Month 12, YR (Year 99. DW: Day of the Week Register This register provides a Day of the Week status ...

Page 12

REG ADDR. TYPE NAME 7 003F Status SR BAT 0037 RTC Y2K 0 (SRAM) 0036 DW 0 0035 YR Y23 0034 MO 0 0033 DT 0 0032 HR MIL 0031 MN 0 0030 SC 0 0014 Control PWR SBIB (EEPROM ...

Page 13

Alarm Registers (Non-Volatile) Alarm0 and Alarm1 The alarm register bytes are set up identical to the RTC register bytes, except that the MSB of each byte functions as an enable bit (enable = “1”). These enable bits specify which alarm ...

Page 14

TABLE 4. DIGITAL TRIMMING REGISTERS DTR REGISTER ESTIMATED FREQUENCY DTR2 DTR1 DTR0 PWR Register: SBIB, BSW, ...

Page 15

... Many types of batteries can be used with Intersil RTC products. For example, 3.0V or 3.6V Lithium batteries are appropriate, and battery sizes are available that can power an Intersil RTC device for years. Another option is to use a SuperCap for applications where V for month. See “Application Section” on page 22 for more information ...

Page 16

Standard Mode Power Switchover • Normal Operating Mode ( Battery Backup Mode BAT To transition from the mode, both of the DD BAT following conditions must be met: • Condition 1: V ...

Page 17

Watchdog Timer Operation The Watchdog timer timeout period is selectable. By writing a value to WD1 and WD0, the Watchdog timer can be set to 3 different time out periods or off. When the Watchdog timer is set to off, ...

Page 18

SCL SDA DATA STABLE FIGURE 16. VALID DATA CHANGES ON THE SDA BUS SCL SDA FIGURE 17. VALID START AND STOP CONDITIONS SCL FROM MASTER DATA OUTPUT FROM TRANSMITTER DATA OUTPUT FROM RECEIVER START FIGURE 18. ACKNOWLEDGE RESPONSE FROM RECEIVER ...

Page 19

Device Addressing Following a start condition, the master must output a Slave Address Byte. The first 4 bits of the Slave Address Byte specify access to either the EEPROM array or to the CCR. Slave bits ‘1010’ access the EEPROM ...

Page 20

SIGNALS FROM THE MASTER SDA BUS SIGNALS FROM THE SLAVE 6 BYTES ADDRESS = 5 ADDRESS POINTER ENDS AT ADDR = 5 FIGURE 21. WRITING 12 BYTES TO A 16-BYTE MEMORY PAGE STARTING AT ADDRESS SIGNALS FROM ...

Page 21

S T SIGNALS FROM SLAVE A THE MASTER R ADDRESS T SDA BUS SIGNALS FROM C THE SLAVE K FIGURE 23. CURRENT ADDRESS READ SEQUENCE BYTE LOAD COMPLETED BY ISSUING STOP. ENTER ACK POLLING ...

Page 22

... EEPROM. Extremely low overall temperature drift is possible with this method. The Intersil evaluation board contains the circuitry necessary to implement this control. Layout Considerations The crystal input at X1 has a very high impedance and will pick up high frequency signals from other circuits on the board ...

Page 23

... Backup Battery Operation Many types of batteries can be used with the Intersil RTC products. 3.0V or 3.6V Lithium batteries are appropriate, and sizes are available that can power a Intersil RTC device for years. Another option is to use a supercapacitor for applications where V short periods of time. Depending on the value of ...

Page 24

A simple silicon or Schottky barrier diode can be used in series with V DD supercapacitor, which is connected to the V use Schottky diodes ...

Page 25

C, LV RESET, AND BATTERY BACKUP OPERATION SUMMARY (Shaded Row is same as X12028 operation) 2 TABLE 10 BAT SBIB BSW SWITCHOVER MODE BIT BIT VOLTAGE Standard Mode 2.2V TRIP typ Default ...

Page 26

Alarm Operation Examples Following are examples of both Single Event and periodic Interrupt Mode alarms. EXAMPLE 1 Alarm 0 set with single interrupt (IM=”0”) A single alarm will occur on January 1 at 11:30am. A. Set Alarm 0 registers as ...

Page 27

Package Outline Drawing M8.173 8 LEAD THIN SHRINK SMALL OUTLINE PACKAGE (TSSOP) Rev 2, 01/ 3.0 ±0 4.40 ±0. PIN 1 ID MARK 1 0. 0.65 TOP VIEW H C ...

Page 28

... Accordingly, the reader is cautioned to verify that data sheets are current before placing orders. Information furnished by Intersil is believed to be accurate and reliable. However, no responsibility is assumed by Intersil or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use ...