HD3-6408-9Z Intersil, HD3-6408-9Z Datasheet - Page 4

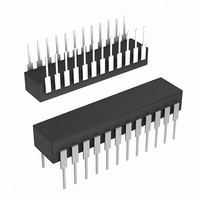

HD3-6408-9Z

Manufacturer Part Number

HD3-6408-9Z

Description

IC ASMA ADT CMOS 1.25MHZ 24DIP

Manufacturer

Intersil

Type

Manchester Encoder/Decoderr

Datasheet

1.HD3-6408-9Z.pdf

(11 pages)

Specifications of HD3-6408-9Z

Applications

Security Systems

Voltage - Supply, Analog

4.5 V ~ 5.5 V

Voltage - Supply, Digital

4.5 V ~ 5.5 V

Mounting Type

Through Hole

Package / Case

24-DIP (0.600", 15.24mm)

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

HD3-6408-9Z

Manufacturer:

Intersil

Quantity:

30

Encoder Operation

The Encoder requires a single clock with a frequency of

twice the desired data rate applied at the SClock input. An

auxiliary divide by six counter is provided on chip which can

be utilized to produce the SClock by dividing the DClock.

The Encoder’s cycle begins when EE is high during a falling

edge of ESC (1). This cycle lasts for one word length or

twenty ESC periods. At the next low-to-high transition of the

ESC, a high at SS input actuates a Command sync or a low

will produce a Data sync for that word (2). When the Encoder

is ready to accept data, the SD output will go high and

remain high for sixteen ESC periods (3) - (4).

During these sixteen periods the data should be clocked into

the SD Input with every high-to-low transition of the ESC (3)

TIMING

BOO

ESC

BZO

SCI

SDI

SD

EE

SS

1

VALID

2

1ST HALF

SYNC

0

4

1

2ND HALF

SYNC

3

2

15

DON’T CARE

15

15

DON’T CARE

3

14

14

14

4

13

13

13

5

HD-6408

12

12

12

6

11

- (4). After the sync and Manchester II encoded data are

transmitted through the BOO and BZO outputs, the Encoder

adds on an additional bit which is the (odd) parity for that

word (5). If ENCODER ENABLE is held high continuously,

consecutive words will be encoded without an interframe

gap. ENCODER ENABLE must go low by time (5) as shown

to prevent a consecutive word from being encoded. At any

time a low on OI will force both bipolar outputs to a high state

but will not affect the Encoder in any other way.

To Abort the Encoder transmission a positive pulse must be

applied at MR. Any time after or during this pulse, a low-to-

high transition on SCI clears the internal counters and

initializes the Encoder for a new word.

11

11

7

10

3

15

3

3

2

16

2

2

1

17

1

1

0

18

0

0

4

5

19

P

P

March 7, 2006

FN2952.2