ISPLSI1016EA LATTICE [Lattice Semiconductor], ISPLSI1016EA Datasheet

ISPLSI1016EA

Available stocks

Related parts for ISPLSI1016EA

ISPLSI1016EA Summary of contents

Page 1

Features • HIGH-DENSITY PROGRAMMABLE LOGIC — 2000 PLD Gates — 32 I/O Pins, One Dedicated Input — 96 Registers — High-Speed Global Interconnect — Wide Input Gating for Fast Counters, State Machines, Address Decoders, etc. — Small Logic Block Size ...

Page 2

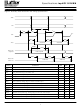

Functional Block Diagram Figure 1. ispLSI 1016EA Functional Block Diagram VCCIO I/O 0 I/O 1 I/O 2 I/O 3 I/O 4 I/O 5 I/O 6 I/O 7 I/O 8 I/O 9 I/O 10 I/O 11 I/O 12 I/O 13 I/O ...

Page 3

Boundary Scan Figure 2. Boundary Scan Waveforms and Timing Specifications TMS TDI T btch TCK TDO Data to be captured Data to be driven out Symbol t TCK [BSCAN test] clock pulse width btcp t TCK [BSCAN test] pulse width ...

Page 4

Absolute Maximum Ratings Supply Voltage V ................................ -0.5 to +7.0V CC Input Voltage Applied ........................ -2 Off-State Output Voltage Applied ..... -2 Storage Temperature ................................ -65 to 150 C Case Temp. with Power Applied .............. -55 ...

Page 5

Switching Test Conditions Input Pulse Levels Input Rise and Fall Time 10% to 90% Input Timing Reference Levels Output Timing Reference Levels Output Load 3-state levels are measured 0.5V from steady-state active level. Output Load Conditions (see Figure 3) TEST ...

Page 6

External Timing Parameters 4 TEST 2 # PARAMETER COND Data Propagation Delay, 4PT Bypass, ORP Bypass pd1 Data Propagation Delay, Worst Case Path pd2 Clock Frequency with Internal Feedback max (Int.) ...

Page 7

Internal Timing Parameters 2 PARAM. # Inputs t 22 I/O Register Bypass iobp t 23 I/O Latch Delay iolat t 24 I/O Register Setup Time before Clock iosu t 25 I/O Register Hold Time after Clock ioh t 26 I/O ...

Page 8

Internal Timing Parameters PARAM. # Outputs t 49 Output Buffer Delay Output Buffer Delay, Slew Limited Adder I/O Cell OE to Output Enabled oen t 52 I/O Cell OE to Output Disabled odis t ...

Page 9

Timing Model I/O Cell Ded. In #28 I/O Reg Bypass I/O Pin #22 (Input) Input GRP Loading Register D Q RST #29 #59 # Reset Y1 Y0 GOE Derivations ...

Page 10

Maximum GRP Delay vs GLB Loads Power Consumption Power consumption in the ispLSI 1016EA device de- pends on two primary factors: the speed at which the device is operating and the number of Product Terms Figure 4. Typical Device Power ...

Page 11

Pin Description PLCC NAME PIN NUMBERS I I/O 3 15, 16, 17, 18, I I/O 7 19, 20, 21, 22, 13, 19, I I/O 11 25, 26, 27, 28, 23, I I/O ...

Page 12

Pin Configurations ispLSI 1016EA 44-Pin PLCC Pinout Diagram I/O 28 I/O 29 I/O 30 I/O 31 VCCIO 1. Pins have dual function capability which is software selectable. ispLSI 1016EA 44-Pin TQFP Pinout Diagram I/O 28 I/O 29 I/O 30 I/O ...

Page 13

Part Number Description ispLSI Device Family Device Number Speed 200 = 200 MHz f max 125 = 125 MHz f max 100 = 100 MHz f max ispLSI 1016EA Ordering Information FAMILY fmax (MHz) tpd (ns) 200 200 125 ispLSI ...