PSD913212JIT ST Microelectronics, PSD913212JIT Datasheet - Page 73

PSD913212JIT

Manufacturer Part Number

PSD913212JIT

Description

Flash In-System Programmable ISP Peripherals For 8-bit MCUs

Manufacturer

ST Microelectronics

Datasheet

1.PSD913212JIT.pdf

(94 pages)

- Current page: 73 of 94

- Download datasheet (477Kb)

Preliminary Information

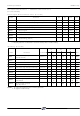

Write Timing

PLD Combinatorial Timing

NOTE: 1. Fast Slew Rate output available on PA[3:0], PB[3:0], and PD[2:0].

NOTES: 1.

Microcontroller Interface – PSD9XX AC/DC Parameters

(5V ± 10% Versions)

Symbol

t

t

Symbol

PD

ARD

t

t

t

t

t

t

t

t

t

t

t

t

LVLX

AVLX

LXAX

AVWL

SLWL

DVWH

WHDX

WLWH

WHAX1

WHAX2

WHPV

AVPV

2.

3.

4.

PLD Input Pin/Feedback

to PLD Combinatorial

Output

PLD Array Delay

Any input used to select an internal PSD9XX function.

In multiplexed mode, latched addresses generated from ADIO delay to address output on any Port.

WR timing has the same timing as E, LDS, UDS, WRL, and WRH signals.

Address Hold Time for DPLD inputs that are used to generate chip selects for internal PSD memory.

ALE or AS Pulse Width

Address Setup Time

Address Hold Time

Address Valid to Leading Edge of WR

CS Valid to Leading Edge of WR

WR Data Setup Time

WR Data Hold Time

WR Pulse Width

Trailing Edge of WR to Address Invalid

Trailing Edge of WR to DPLD Address

Input Invalid

Trailing Edge of WR to Port Output

Valid Using I/O Port Data Register

Address Input Valid to Address

Output Delay

(5 V ± 10% Versions)

Parameter

Parameter

(5 V ± 10%)

Micro Cell

Conditions Min

Any

-70

(Notes 1 and 3)

(Note 3 and 4)

Conditions

Max

20

(Note 1)

(Note 1)

(Note 3)

(Note 3)

(Note 3)

(Note 3)

(Note 3)

(Note 3)

(Note 2)

11

Min

-90

Max

25

16

Min

15

12

25

31

4

7

8

4

6

0

-70

Min

Max

-15

27

20

Max

32

22

Min

20

15

15

35

35

6

8

5

8

0

Add 2

Add 2

-90

Fast

Aloc

PT

Max

30

25

TURBO

Add 10 Sub 2

OFF

Min

28

10

20

20

45

45

10

11

5

0

-15

PSD9XX Family

(Note 1)

Slew

Rate

Max

38

30

Unit

Unit

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

69

Related parts for PSD913212JIT

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

120V - 100W DMOS AUDIO AMPLIFIER WITH MUTE/ST-BY

Manufacturer:

ST Microelectronics

Datasheet:

Part Number:

Description:

Manufacturer:

ST Microelectronics

Datasheet:

Part Number:

Description:

N-channel 55V - 0.07 Ohm - 22A StripFET Power MOSFET

Manufacturer:

ST Microelectronics, Inc.

Datasheet:

Part Number:

Description:

Old PRODUCT: Not Suitable For Design-in

Manufacturer:

ST Microelectronics, Inc.

Datasheet:

Part Number:

Description:

Programmable poly-phase energy calculator IC

Manufacturer:

ST Microelectronics

Datasheet:

Part Number:

Description:

High-voltage, High Current Switch

Manufacturer:

ST Microelectronics, Inc.

Datasheet:

Part Number:

Description:

Single Chip Read & Write Channel

Manufacturer:

ST Microelectronics, Inc.

Datasheet:

Part Number:

Description:

10A Triacs

Manufacturer:

ST Microelectronics, Inc.

Datasheet:

Part Number:

Description:

20A Triacs

Manufacturer:

ST Microelectronics, Inc.

Datasheet:

Part Number:

Description:

-

Manufacturer:

ST Microelectronics, Inc.

Datasheet:

Part Number:

Description:

ac Line Switch

Manufacturer:

ST Microelectronics, Inc.

Datasheet:

Part Number:

Description:

Video And Audio Signals Switchings For The Peri-television Plug

Manufacturer:

ST Microelectronics, Inc.

Datasheet:

Part Number:

Description:

H/v Deflection With Automatic VCR Switching

Manufacturer:

ST Microelectronics, Inc.

Datasheet:

Part Number:

Description:

Switch Mode Power Supply Controller

Manufacturer:

ST Microelectronics, Inc.

Datasheet:

Part Number:

Description:

Stepper Motor Driver

Manufacturer:

ST Microelectronics, Inc.

Datasheet: