PSD913F1-B-90JI ST Microelectronics, PSD913F1-B-90JI Datasheet - Page 14

PSD913F1-B-90JI

Manufacturer Part Number

PSD913F1-B-90JI

Description

Flash In-System Programmable ISP Peripherals For 8-bit MCUs

Manufacturer

ST Microelectronics

Datasheet

1.PSD913F1-B-90JI.pdf

(94 pages)

- Current page: 14 of 94

- Download datasheet (477Kb)

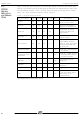

7.0

Table 5.

PSD9XX

Pin

Descriptions

10

PSD9XX Family

The following table describes the pin names and pin functions of the PSD9XX. Pins that

have multiple names and/or functions are defined using PSDsoft.

Pin Name

ADIO0-7

ADIO8-15

CNTL0

CNTL1

(PLCC)

Pin* Type

30-37

39-46

47

50

I/O

I/O

I

I

This is the lower Address/Data port. Connect your MCU

address or address/data bus according to the following rules:

1. If your MCU has a multiplexed address/data bus where

2. If your MCU does not have a multiplexed address/data

3. If you are using an 80C51XA in burst mode, connect

ALE or AS latches the address. The PSD drives data out only

if the read signal is active and one of the PSD functional

blocks was selected. The addresses on this port are passed

to the PLDs.

This is the upper Address/Data port. Connect your MCU

address or address/data bus according to the following rules:

1. If your MCU has a multiplexed address/data bus where

2. If your MCU does not have a multiplexed address/data

3. If you are using an 80C251 in page mode, connect

4. If you are using an 80C51XA in burst mode, connect

ALE or AS latches the address. The PSD drives data out only

if the read signal is active and one of the PSD functional

blocks was selected. The addresses on this port are passed

to the PLDs.

The following control signals can be connected to this port,

based on your MCU:

1. WR — active-low write input.

2. R_W — active-high read/active low write input.

This pin is connected to the PLDs. Therefore, these signals

can be used in decode and other logic equations.

The following control signals can be connected to this port,

based on your MCU:

1. RD — active-low read input.

2. E — E clock input.

3. DS — active-low data strobe input.

4. PSEN — connect PSEN to this port when it is being used

the data is multiplexed with the lower address bits,

connect AD[0:7] to this port.

bus, or you are using an 80C251 in page mode, connect

A[0:7] to this port.

A4/D0 through A11/D7 to this port.

the data is multiplexed with the lower address bits,

connect A[8:15] to this port.

bus, connect A[8:15] to this port.

AD[8:15] to this port.

A12/D8 through A19/D15 to this port.

as an active-low read signal. For example, when the

80C251 outputs more than 16 address bits, PSEN is

actually the read signal.

This pin is connected to the PLDs. Therefore, these

signals can be used in decode and other logic equations.

Description

Preliminary Information

Related parts for PSD913F1-B-90JI

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

120V - 100W DMOS AUDIO AMPLIFIER WITH MUTE/ST-BY

Manufacturer:

ST Microelectronics

Datasheet:

Part Number:

Description:

Manufacturer:

ST Microelectronics

Datasheet:

Part Number:

Description:

N-channel 55V - 0.07 Ohm - 22A StripFET Power MOSFET

Manufacturer:

ST Microelectronics, Inc.

Datasheet:

Part Number:

Description:

Old PRODUCT: Not Suitable For Design-in

Manufacturer:

ST Microelectronics, Inc.

Datasheet:

Part Number:

Description:

Programmable poly-phase energy calculator IC

Manufacturer:

ST Microelectronics

Datasheet:

Part Number:

Description:

High-voltage, High Current Switch

Manufacturer:

ST Microelectronics, Inc.

Datasheet:

Part Number:

Description:

Single Chip Read & Write Channel

Manufacturer:

ST Microelectronics, Inc.

Datasheet:

Part Number:

Description:

10A Triacs

Manufacturer:

ST Microelectronics, Inc.

Datasheet:

Part Number:

Description:

20A Triacs

Manufacturer:

ST Microelectronics, Inc.

Datasheet:

Part Number:

Description:

-

Manufacturer:

ST Microelectronics, Inc.

Datasheet:

Part Number:

Description:

ac Line Switch

Manufacturer:

ST Microelectronics, Inc.

Datasheet:

Part Number:

Description:

Video And Audio Signals Switchings For The Peri-television Plug

Manufacturer:

ST Microelectronics, Inc.

Datasheet:

Part Number:

Description:

H/v Deflection With Automatic VCR Switching

Manufacturer:

ST Microelectronics, Inc.

Datasheet:

Part Number:

Description:

Switch Mode Power Supply Controller

Manufacturer:

ST Microelectronics, Inc.

Datasheet:

Part Number:

Description:

Stepper Motor Driver

Manufacturer:

ST Microelectronics, Inc.

Datasheet: