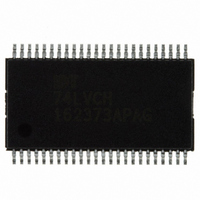

IDT74LVCH162373APAG8 IDT, Integrated Device Technology Inc, IDT74LVCH162373APAG8 Datasheet

IDT74LVCH162373APAG8

Specifications of IDT74LVCH162373APAG8

800-1678-2

Related parts for IDT74LVCH162373APAG8

IDT74LVCH162373APAG8 Summary of contents

Page 1

IDT74LVCH162373A 3.3V CMOS 16-BIT TRANSPARENT D-TYPE LATCH FEATURES: • Typical t (Output Skew) < 250ps SK(o) • ESD > 2000V per MIL-STD-883, Method 3015; > 200V using machine model (C = 200pF • 3.3V ± ...

Page 2

IDT74LVCH162373A 3.3V CMOS 16-BIT TRANSPARENT D-TYPE LATCH PIN CONFIGURATION GND ...

Page 3

IDT74LVCH162373A 3.3V CMOS 16-BIT TRANSPARENT D-TYPE LATCH DC ELECTRICAL CHARACTERISTICS OVER OPERATING RANGE Following Conditions Apply Unless Otherwise Specified: Operating Condition –40°C to +85°C A Symbol Parameter V Input HIGH Voltage Level IH V Input LOW Voltage Level ...

Page 4

IDT74LVCH162373A 3.3V CMOS 16-BIT TRANSPARENT D-TYPE LATCH OUTPUT DRIVE CHARACTERISTICS Symbol Parameter V Output HIGH Voltage OH V Output LOW Voltage OL NOTE and V must be within the min. or max. range shown in the DC ELECTRICAL ...

Page 5

IDT74LVCH162373A 3.3V CMOS 16-BIT TRANSPARENT D-TYPE LATCH TEST CIRCUITS AND WAVEFORMS TEST CONDITIONS (1) (1) Symbol V = 3.3V±0. 2. LOAD V 2.7 2 1.5 1 300 300 LZ ...

Page 6

IDT74LVCH162373A 3.3V CMOS 16-BIT TRANSPARENT D-TYPE LATCH ORDERING INFORMATION LVC Bus-Hold Family Temp. Range CORPORATE HEADQUARTERS 6024 Silver Creek Valley Road San Jose, CA 95138 XX XXXX Device Type Package PV PVG PA PAG 373A 162 H ...