DS34T108GN+ Maxim Integrated Products, DS34T108GN+ Datasheet - Page 11

DS34T108GN+

Manufacturer Part Number

DS34T108GN+

Description

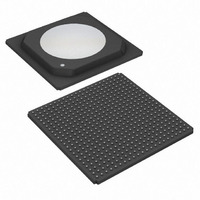

IC TDM OVER PACKET 484HSBGA

Manufacturer

Maxim Integrated Products

Type

TDM (Time Division Multiplexing)r

Datasheet

1.DS34T108GN.pdf

(16 pages)

Specifications of DS34T108GN+

Applications

Data Transport

Mounting Type

Surface Mount

Package / Case

484-BGA Exposed Pad, 484-eBGA, 484-HBGA

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

TDMoP Bundles

TDMoP Clock Recovery

TDMoP Delay Variation Compensation

____________________________________________________ DS34T101, DS34T102, DS34T104, DS34T108

64 independent bundles, each can be assigned to any TDM interface

Each bundle carries a data stream from one TDM interface over IP/MPLS/Ethernet PSN from TDMoP source

device to TDMoP destination device

Each bundle may be for N x 64kbps, an entire E1, T1, E3, T3 or STS-1, or an arbitrary serial data stream

Each bundle is uni-directional (but frequently coupled with opposite-direction bundle for bidirectional

communication)

Multiple bundles can be transported between TDMoP devices

Multiple bundles can be assigned to the same TDM interface

Each bundle is independently configured with its own:

Each bundle can be assigned to one of the payload-type machines or to the CPU

For E1/T1 the device provides internal bundle cross-connect functionality, with DS0 resolution

Sophisticated TDM clock recovery machines, one for each TDM interface, allow end-to-end TDM clock

synchronization, despite the packet delay variation of the IP/MPLS/Ethernet network

The following clock recovery modes are supported:

The clock recovery machines provide both fast frequency acquisition and highly accurate phase tracking:

Configurable jitter buffers compensate for delay variation introduce by the IP/MPLS/Ethernet network

Large maximum jitter buffer depths:

Packet reordering is performed for SAToP and CESoPSN bundles within the range of the jitter buffer

Packet loss is compensated by inserting either a pre-configured conditioning value or the last received value.

o

o

o

o

o

o

o

o

o

o

o

o

o

o

o

o

o

o

o

o

o

Transmit and receive queues

Configurable receive-buffer depth

Optional connection-level redundancy (SAToP, AAL1, CESoPSN only).

Adaptive clock recovery

Common clock (using RTP)

External clock

Loopback clock

Jitter and wander of the recovered clock are maintained at levels that conform to G.823/G.824 traffic or

synchronization interfaces. (For adaptive clock recovery, the recovered clock performance depends on

packet network characteristics.)

Short-term frequency accuracy (1 second) is better than 16 ppb (using OCXO reference), or 100 ppb

(using TCXO reference)

Capture range is ±90 ppm

Internal synthesizer frequency resolution of 0.5 ppb

High resilience to packet loss and misordering, up to 2% without degradation of clock recovery

performance

Robust to sudden significant constant delay changes

Automatic transition to holdover when link break is detected

E1: up to 256 ms

T1 unframed: up to 340 ms

T1 framed: up to 256 ms

T1 framed with CAS: up to 192 ms

E3: up to 60 ms

T3: up to 45 ms

STS-1: up to 40 ms.

11 of 16