DS34T108GN+ Maxim Integrated Products, DS34T108GN+ Datasheet - Page 12

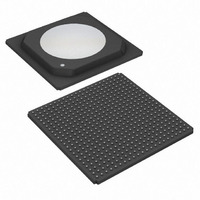

DS34T108GN+

Manufacturer Part Number

DS34T108GN+

Description

IC TDM OVER PACKET 484HSBGA

Manufacturer

Maxim Integrated Products

Type

TDM (Time Division Multiplexing)r

Datasheet

1.DS34T108GN.pdf

(16 pages)

Specifications of DS34T108GN+

Applications

Data Transport

Mounting Type

Surface Mount

Package / Case

484-BGA Exposed Pad, 484-eBGA, 484-HBGA

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

TDMoP CAS Support

Test and Diagnostics

CPU Interface

____________________________________________________ DS34T101, DS34T102, DS34T104, DS34T108

On-chip CAS handler terminates E1/T1 CAS when using AAL1/CESoPSN in structured-with-CAS mode.

CPU intervention is not required for CAS handling.

IEEE 1149.1 JTAG support

Per-channel programmable on-chip bit error-rate testing (BERT)

Pseudorandom patterns including QRSS

User-defined repetitive patterns

Error insertion single and continuous

Total-bit and errored-bit counts

Payload error insertion

Error insertion in the payload portion of the T1 and E1 frame in the transmit path

Errors can be inserted over the entire frame or selected channels

Insertion options include continuous and absolute number with selectable insertion rates

F-bit corruption for line testing

Loopbacks (remote, local, analog, and per-channel loopback)

MBIST (memory built-in self test)

32 or 16-bit parallel interface or optional SPI serial interface

Byte write enable pins for single-byte write resolution

Hardware reset pin

Software reset supported

Software access to device ID and silicon revision

On-chip SDRAM controller provides access to SDRAM for both the chip and the CPU

CPU can access transmit and receive buffers in SDRAM used for packets to/from the CPU (ARP, SNMP, etc.)

12 of 16