HSC-ADC-EVALCZ Analog Devices Inc, HSC-ADC-EVALCZ Datasheet

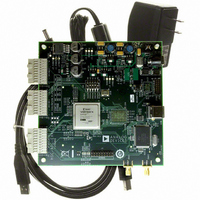

HSC-ADC-EVALCZ

Specifications of HSC-ADC-EVALCZ

Available stocks

Related parts for HSC-ADC-EVALCZ

HSC-ADC-EVALCZ Summary of contents

Page 1

... SPI. The ADC capture board supports these SPI-driven features through the existing USB connection to the computer without additional cabling needed. 6. VisualAnalog™. VisualAnalog supports the HSC-ADC- EVALC hardware platform as well as enabling virtual ADC evaluation using ADIsimADC™, Analog Devices proprietary behavioral modeling technology. This allows rapid compari- son between multiple ADCs, with or without hardware evaluation boards ...

Page 2

... Equipment Needed........................................................................... 1 Product Highlights ........................................................................... 1 Functional Block Diagram .............................................................. 1 Revision History ............................................................................... 2 Product Description......................................................................... 3 Evaluation Board Description......................................................... 3 Evaluation Board Hardware ............................................................ 4 HSC-ADC-EVALC ADC Capture Board Easy Start ............... 4 Power Supplies .............................................................................. 4 Connection and Setup ................................................................. 4 Jumpers .......................................................................................... 5 HSC-ADC-EVALC ADC Capture Board Features.................. 6 HSC-ADC-EVALC Supported ADC Evaluation Boards........ 7 REVISION HISTORY 4/07— ...

Page 3

... I/O logic levels can be selected by proper connection of various jumpers or switches (see Table 1). When using the HSC-ADC-EVALC in conjunction with an ADC evaluation board critical that the signal sources used for the ADC board’s analog input and clock have very low phase noise (< ...

Page 4

... The other end is a 2.1 mm inner diameter jack that connects to the PCB at J4. 6. Once the USB cable is connected to both the computer and the HSC-ADC-EVALC board, and power is applied, the USB driver starts to install. The Found New Hardware Wizard opens and prompts you through the automated install process. ...

Page 5

... SIGNAL SYNTHESIZER ROHDE & SCHWARZ, SMHU, 2V p-p SIGNAL SYNTHESIZER Figure 2. Example Setup Using ADC Evaluation Board and HSC-ADC-EVALC ADC Capture Board JUMPERS Default Settings Table 1 lists the default settings for the HSC-ADC-EVALC evaluation kit. Table 1. Jumper Configurations Jumper Number J9, Pin 1 to Pin 2 (1.8 V) J9, Pin 3 to Pin 4 (2 ...

Page 6

... FPGA DEBUG PINS EXTERNAL SYNC I/O CYPRESS USB CONTROLLER DATA BUS 1 DATA BUS 2 USB CONNECTOR FPGA JTAG CONNECTOR Figure 3. HSC-ADC-EVALC Components (Top View) Rev Page FPGA LOAD SELECT ON BOARD POWER SUPPLY 100MHz OSCILLATOR FPGA I/O VOLTAGE MODE FPGA CONFIG PROM 5VDC POWER ...

Page 7

... Some legacy ADC boards may require interposer cards to facilitate proper pin mapping to the ADC capture board. If needed, the interposer part number is noted in the compatibility table at Figure 4. HSC-ADC-EVALC Components (Bottom View) www.analog.com/FIFO www.analog.com/FIFO Rev Page HSC-ADC-EVALC for a list of HSC-ADC-EVALC-compatible ADC for the respective data converter. ...

Page 8

... These clock signals are normally provided by the attached ADC evaluation board and are passed along with the data through one or more pins on Connector J2 and/or Connector J3. Refer to the HSC-ADC-EVALC I/O connector pin mappings shown in Figure 21 and Figure 22. DATA CAPTURE The process of filling the FIFO and reading the data back requires several steps ...

Page 9

... EVALUATION BOARD SCHEMATICS AND ARTWORK HSC-ADC-EVALC SCHEMATICS TYCO AND DSP EZ–KIT CONNECTOR TO FPGA XC4VFX20-10FFG672C R50 51.1Ω XC4VFX20-10FFG672C XC4VFX20-10FFG672C XC4VFX20-10FFG672C R38 100Ω R39 100Ω Figure 5. Rev Page HSC-ADC-EVALC ...

Page 10

... HSC-ADC-EVALC R1 100Ω R40 R44 R42 3.74KΩ 3.74KΩ 3.74KΩ SRAM ADDRESS AND CONTROL 249Ω R28 3.74KΩ 249Ω U21 FPGA CONTROLS NC7SZ05M5X R41 R43 3.74KΩ 3.74KΩ Figure 6. Rev Page R27 R33 XC4VFX20-10FFG672C R25 3.74KΩ ...

Page 11

... FPGA TO SRAM DATA XC4VFX20-10FFG672C XC4VFX20-10FFG672C Figure 7. Rev Page HSC-ADC-EVALC ...

Page 12

... HSC-ADC-EVALC AD19 TO BE USED WITH HIGHER DENSITY SRAM DEVICES Figure 8. Rev Page ...

Page 13

... SRAM AND FPGA POWER R63 499Ω R65 499Ω XC4VFX20-10FFG672C Figure 9. Rev Page HSC-ADC-EVALC R64 499Ω R66 499Ω XC4VFX20-10FFG672C ...

Page 14

... HSC-ADC-EVALC SRAM A BYPASS CAP SRAM B BYPASS CAP REFCLK Oscillator for IDELAYCTRL FPGA BYPASS CAP Figure 10. Rev Page R15 24Ω ...

Page 15

... UNUSED ROCKET I/0 CONNECTIONS XC4VFX20-10FFG672C DEBUG PINS Figure 11. Rev Page HSC-ADC-EVALC XC4VFX20-10FFG672C ...

Page 16

... HSC-ADC-EVALC ROCKET I/0 CONNECTIONS Figure 12. Rev Page ...

Page 17

... USB CONNECTIONS Figure 13. Rev Page HSC-ADC-EVALC R49 R71 3.74Ω 3.74Ω R48 100KΩ SDI & SDO DIRECTIONS ARE WITH RESPECT TO THE DEVICE UNDER CONTROL. ...

Page 18

... HSC-ADC-EVALC R46 499Ω USB CONNECTIONS (CONTINUED) J6 R52 R72 3.74KΩ 3.74KΩ XC4VFX20-10FFG672C Figure 14. Rev Page XC4VFX20-10FFG672C ...

Page 19

... EZ–KIT EXPANSION INTERFACE – FOR DSPs P1 P2 Figure 15. Rev Page HSC-ADC-EVALC P3 ...

Page 20

... HSC-ADC-EVALC , Figure 16. Rev Page 06676-016 ...

Page 21

... CONFIGURATION EEPROM R77 100Ω R78 100Ω R75 3.74KΩ R76 3.74KΩ JTAG CONNECTOR Figure 17. Rev Page HSC-ADC-EVALC R73 ZERO EEPROM HARDWARE RECONFIGURATION PUSHBUTTON R57 3.74KΩ ...

Page 22

... HSC-ADC-EVALC + + + + + + + REMOVE NOT DO Figure 18. Rev Page 06676-018 + + ...

Page 23

... EXTERNAL SYNC I/O CYPRESS USB CONTROLLER DATA BUS 1 DATA BUS 2 USB CONNECTOR FPGA JTAG CONNECTOR Figure 19. Top Silkscreen Figure 20. Bottom Silkscreen Rev Page HSC-ADC-EVALC FPGA LOAD SELECT ON BOARD POWER SUPPLY 100MHz OSCILLATOR FPGA I/O VOLTAGE MODE FPGA CONFIG PROM 5VDC POWER ...

Page 24

... HSC-ADC-EVALC I/O CONNECTOR—J1, J2, AND J3 PIN MAPPING 06676-021 Figure 21. J2 and J3 Pin Mapping Rev Page ...

Page 25

... I/O_5 I/O_7 SCLK SDI SDO I/O_4 I/O_6 I/O_8 CSB_1 CSB_2 CSB_3 (J1) HS-SERIAL/SPI/AUX Figure 22. J1 Pin Mapping 32mm J2 J3 DATA BUS 1 Rev Page HSC-ADC-EVALC SD7– SD8– MGTCLK2– SD7+ SD8+ MGTCLK2+ USB_1 USB_2 USB_4 CSB_4 USB_3 USB_5 43.155mm DATA BUS 2 ...

Page 26

... SD3− A8 I/O_6 B8 I/O_5 C8 SD2+ D8 SD2− A9 I/O_4 B9 I/O_3 C9 SD1+ D9 SD1− A10 I/O_2 B10 I/O_1 C10 MGTCLK1+ D10 MGTCLK1− Table 4. HSC-ADC-EVALC J2 I/O Connections to FPGA (U1) Connector J2 FPGA Pin (DATA BUS 1) none A1 none B1 AF10 C1 AF11 D1 none A2 none B2 none C2 none D2 none A3 none B3 none ...

Page 27

... Table 5. HSC-ADC-EVALC J3 I/O Connections to FPGA (U1) Connector J3 (DATA BUS 2) Schematic Net Name A1 DCLKA2+ B1 DCLKA2− C1 D0A+ D1 D0A− A2 D1A+ B2 D1A− C2 D2A+ D2 D2A− A3 D3A+ B3 D3A− C3 D4A+ D3 D4A− A4 D5A+ B4 D5A− C4 D6A+ D4 D6A− A5 D7A+ B5 D7A− C5 D8A+ D5 D8A− ...

Page 28

... HSC-ADC-EVALC ORDERING INFORMATION BILL OF MATERIALS (RoHS COMPLIANT) Table 6. Qty Reference Designator Description 1 PCB PCB, ADC evaluation platform 0 BGA1, BGA2 IC, 18-bit DDRII SRAM 2-word burst operation (MOS integrated circuit), do not install 2 C1, C2 Capacitor, 470 pF ceramic X7R 0402 3 C10, C17, C33 Capacitor, 330 μ SMD ...

Page 29

... Analog Devices ECS Xilinx National Semiconductor Connor-Winfield Corp. Epson Electronics America Analog Devices Fairchild Semiconductor Cypress Semiconductor Corp. CTS 2 C bus serial EEPROM Microchip Rev Page HSC-ADC-EVALC Part Number MPZ1608S221A TFM-145-32-S-D-A ERJ-2RKF1000X ERJ-2GEJ240X ERJ-2RKF7502X ERJ-2RKF51R1X ERJ-2RKF4990X ERJ-2RKF4022X ERJ-2RKF3741X ERJ-2RKF1693X ERJ-2RKF2490X ERJ-2RKF1473X ...

Page 30

... C15 0402 chip capacitor, X5R, 6 μF, ±20%, do not install ORDERING GUIDE Model Description HSC-ADC-EVALC Data Converter Evaluation Platform 1 HSC-ADC-EVALCZ Data Converter Evaluation Platform RoHS Compliant Part. Manufacturer Fairchild Semiconductor Analog Devices Alps Richco, Inc. CUI, Inc. Analog Devices ...

Page 31

... NOTES Rev Page HSC-ADC-EVALC ...

Page 32

... HSC-ADC-EVALC NOTES ©2007 Analog Devices, Inc. All rights reserved. Trademarks and registered trademarks are the property of their respective owners. EB06676-0-4/07(0) Rev Page ...