NCP5425SOEVB ON Semiconductor, NCP5425SOEVB Datasheet - Page 16

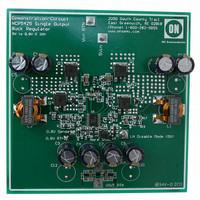

NCP5425SOEVB

Manufacturer Part Number

NCP5425SOEVB

Description

EVAL BOARD FOR NCP5425SO

Manufacturer

ON Semiconductor

Specifications of NCP5425SOEVB

Design Resources

NCP5425SOEVB BOM NCP5425SOEVB Gerber Files NCP5425SOEVB Schematic

Main Purpose

DC/DC, Step Down

Outputs And Type

1, Non-Isolated

Voltage - Output

0.8V

Current - Output

30A

Voltage - Input

4.6 ~ 12 V

Regulator Topology

Buck

Frequency - Switching

300kHz

Board Type

Fully Populated

Utilized Ic / Part

NCP5425

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Power - Output

-

Lead Free Status / Rohs Status

Lead free / RoHS Compliant

For Use With/related Products

NCP5425SO

Other names

NCP5425SOEVBOS

where:

switching MOSFET conduction losses can be calculated by:

where:

switch−on and switch−off, and can be calculated by:

where:

then be calculated as:

where:

known, the maximum FET switch junction temperature can

be calculated:

where:

Once the RMS current through the switch is known, the

Upper MOSFET switching losses occur during MOSFET

The total power dissipation in the switching MOSFET can

Once the total power dissipation in the switching FET is

P HFET(TOTAL) + P RMS(H) ) P SWH(ON) ) P SWH(OFF)

I

I

I

D = duty cycle.

P

I

R

P

P

V

I

T

TFALL = MOSFET fall time (from FET manufacturer’s

T = 1/f

P

P

P

P

T

T

P

R

RMS(H)

L(PEAK)

L(VALLEY)

RMS(H)

OUT

RMS(H)

SWH(ON)

SWH(OFF)

HFET(TOTAL)

RMS(H)

SWH(ON)

SWH(OFF)

A

HFET(TOTAL)

RISE

J

DS(ON)

qJA

IN

= FET junction temperature;

= ambient temperature;

= input voltage;

P SWH + P SWH(ON) ) P SWH(OFF)

= upper FET junction−to−ambient thermal

= load current;

=MOSFET rise time (from FET manufacturer’s

SW

T J + T A ) [ P HFET(TOTAL)

resistance.

switching characteristics performance curve);

= maximum switching MOSFET RMS current;

= maximum switching MOSFET RMS current;

P RMS(H) + I RMS(H) 2

= FET drain−to−source on−resistance.

= switching MOSFET conduction losses;

= upper MOSFET switch conduction Losses;

= inductor peak current;

switching characteristics performance curve);

= upper MOSFET switch−on losses;

= period.

= upper MOSFET switch−on losses;

= upper MOSFET switch−off losses;

= upper MOSFET switch−off losses.

= inductor valley current;

+

= total switching (upper) MOSFET losses;

= total switching (upper) FET losses;

V IN

I OUT

6T

(t RISE ) t FALL )

R DS(ON)

R qJA ]

http://onsemi.com

NCP5425

16

Synchronous (Lower) FET Selection

calculated as follows:

where:

except for losses in the internal body diode, because it turns

on into near zero voltage conditions. The MOSFET body

diode will conduct during the non−overlap time and the

resulting power dissipation (neglecting reverse recovery

losses) can be calculated as follows:

where:

MOSFET can then be calculated as:

where:

is known the maximum FET switch junction temperature

can be calculated:

where:

The switch conduction losses for the lower FET are

The synchronous MOSFET has no switching losses,

The total power dissipation in the synchronous (lower)

Once the total power dissipation in the synchronous FET

P

I

D = Duty Cycle;

R

P

V

I

Non−overlap time = GATE(L)−to−GA TE(H) or

f

P

P

P

T

T

P

R

P SWL + V SD

OUT

LOAD

SW

RMS(L)

SWL

LFET(TOTAL)

RMS(L)

SWL

A

LFET(TOTAL)

J

DS(ON)

qJA

SD

= MOSFET junction temperature;

P RMS(L) + I RMS 2

= ambient temperature;

= switching frequency.

= lower FET source−to−drain voltage;

= load current;

= lower FET junction−to−ambient thermal

= lower FET switching losses;

= Switching losses.

= load current;

P LFET(TOTAL) + P RMS(L) ) P SWL

T J + T A ) [P LFET(TOTAL)

resistance.

= lower MOSFET conduction losses;

= Switch Conduction Losses;

= lower FET drain−to−source on−resistance.

+ I OUT

= total synchronous (lower) FET losses;

= Synchronous (lower) FET total losses;

I LOAD

GATE(H)−to−GA TE(L) delay

(from NCP5425 data sheet

Electrical Characteristics section);

R DS(ON)

(1 * D) 2

non−overlap time

R qJA ]

R DS(ON)

f SW