EVAL-ADT7470EB Analog Devices Inc, EVAL-ADT7470EB Datasheet - Page 19

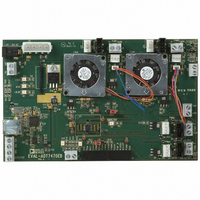

EVAL-ADT7470EB

Manufacturer Part Number

EVAL-ADT7470EB

Description

BOARD EVALUATION FOR ADT7470

Manufacturer

Analog Devices Inc

Datasheet

1.ADT7470ARQZ.pdf

(40 pages)

Specifications of EVAL-ADT7470EB

Sensor Type

Temperature

Interface

SMBus (2-Wire/I²C)

Voltage - Supply

3 V ~ 5.5 V

Embedded

No

Utilized Ic / Part

ADT7470

Lead Free Status / RoHS Status

Contains lead / RoHS non-compliant

Masking Interrupt Sources

Interrupt Mask Register 1 and Interrupt Mask Register 2 are

located at Address 0x72 and Address 0x73. These allow indi-

vidual interrupt sources to be masked out to prevent unwanted

SMBALERT interrupts. Masking an interrupt source prevents

only the SMBALERT output from being asserted; the appro-

priate status bit is still set as usual. This is useful if the system

polls the monitoring devices periodically to determine whether

or not out-of-limit conditions have subsided, without tying up

time-critical system resources.

Table 14. Interrupt Mask Register 1 (Register 0x72)

Bit No.

7

6

5

4

3

2

1

0

Table 15. Interrupt Mask Register 2 (Register 0x73)

Bit No.

7

6

5

4

3

2

1

0

Mnemonic

Unused

R7T

R6T

R5T

R4T

R3T

R2T

R1T

Mnemonic

Fan 4

Fan 3

Fan 2

Fan 1

Unused

R10T

R9T

R8T

Description

Unused.

A 1 masks the SMBALERT for TMP05 Temperature 7.

A 1 masks the SMBALERT for TMP05 Temperature 6.

A 1 masks the SMBALERT for TMP05 Temperature 5.

A 1 masks the SMBALERT for TMP05 Temperature 4.

A 1 masks the SMBALERT for TMP05 Temperature 3.

A 1 masks the SMBALERT for TMP05 Temperature 2.

A 1 masks the SMBALERT for TMP05 Temperature 1.

Description

A 1 masks the SMBALERT for Fan 4 overspeed/underspeed conditions.

A 1 masks the SMBALERT for Fan 3 overspeed/underspeed conditions.

A 1 masks the SMBALERT for Fan 2 overspeed/underspeed conditions.

A 1 masks the SMBALERT for Fan 1 overspeed/underspeed conditions.

Unused.

A 1 masks the SMBALERT for TMP05 Temperature 10.

A 1 masks the SMBALERT for TMP05 Temperature 9.

A 1 masks the SMBALERT for TMP05 Temperature 8.

Rev. C | Page 19 of 40

Enabling the SMBALERT Interrupt Output

The SMBALERT interrupt output is a dedicated function pro-

vided on Pin 14 to signal out-of-limit conditions to a host or

system processor. Because this is a dedicated function, it is

important that limit registers be programmed before monitoring

is enabled to prevent spurious interrupts from occurring on the

SMBALERT pin. Although the SMBALERT output cannot be

specifically disabled, interrupt sources can be masked to prevent

SMBALERT assertions. Monitoring is enabled when Bit 0 (STRT)

of Configuration Register 1 (Register 0x40) is set to 1.

ADT7470