MC56F8323EVM Freescale Semiconductor, MC56F8323EVM Datasheet - Page 137

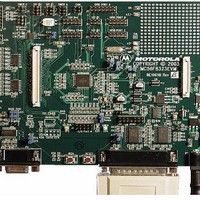

MC56F8323EVM

Manufacturer Part Number

MC56F8323EVM

Description

KIT EVALUATION FOR MC56F8323

Manufacturer

Freescale Semiconductor

Type

DSPr

Datasheets

1.CWH-UTP-ONCE-HE.pdf

(2 pages)

2.MC56F8323EVM.pdf

(72 pages)

3.MC56F8323EVME.pdf

(140 pages)

Specifications of MC56F8323EVM

Contents

Module and Misc Hardware

Processor To Be Evaluated

MC56F8322 and MC56F8323

Data Bus Width

16 bit

Interface Type

RS-232

For Use With/related Products

MC56F8322, MC56F8323

Lead Free Status / RoHS Status

Contains lead / RoHS non-compliant

- Current page: 137 of 140

- Download datasheet (742Kb)

The thermal characterization parameter is measured per JESD51-2 specification using a 40-gauge type T

thermocouple epoxied to the top center of the package case. The thermocouple should be positioned so

that the thermocouple junction rests on the package. A small amount of epoxy is placed over the

thermocouple junction and over about 1mm of wire extending from the junction. The thermocouple wire

is placed flat against the package case to avoid measurement errors caused by cooling effects of the

thermocouple wire.

When heat sink is used, the junction temperature is determined from a thermocouple inserted at the

interface between the case of the package and the interface material. A clearance slot or hole is normally

required in the heat sink. Minimizing the size of the clearance is important to minimize the change in

thermal performance caused by removing part of the thermal interface to the heat sink. Because of the

experimental difficulties with this technique, many engineers measure the heat sink temperature and then

back-calculate the case temperature using a separate measurement of the thermal resistance of the

interface. From this case temperature, the junction temperature is determined from the junction-to-case

thermal resistance.

12.2 Electrical Design Considerations

Use the following list of considerations to assure correct operation of the 56F8323/56F8123:

Freescale Semiconductor

Preliminary

•

•

•

•

•

Provide a low-impedance path from the board power supply to each V

board ground to each V

The minimum bypass requirement is to place six 0.01–0.1μF capacitors positioned as close as possible to

the package supply pins. The recommended bypass configuration is to place one bypass capacitor on each

of the V

performance tolerances.

Ensure that capacitor leads and associated printed circuit traces that connect to the chip V

pins are less than 0.5 inch per capacitor lead

Use at least a four-layer Printed Circuit Board (PCB) with two inner layers for V

Bypass the V

capacitor such as a tantalum capacitor

DD

/V

DD

SS

This device contains protective circuitry to guard

against damage due to high static voltage or electrical

fields. However, normal precautions are advised to

avoid

maximum-rated voltages to this high-impedance circuit.

Reliability of operation is enhanced if unused inputs are

tied to an appropriate voltage level.

pairs, including V

and V

SS

SS

application

layers of the PCB with approximately 100μF, preferably with a high-grade

(GND) pin

56F8323 Technical Data, Rev. 17

DDA

/V

of

SSA.

CAUTION

Ceramic and tantalum capacitors tend to provide better

any

voltages

higher

DD

pin on the device, and from the

than

Electrical Design Considerations

DD

and V

DD

SS

and V

SS

(GND)

137

Related parts for MC56F8323EVM

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet: