MC56F8323EVM Freescale Semiconductor, MC56F8323EVM Datasheet - Page 25

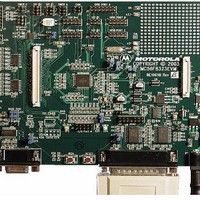

MC56F8323EVM

Manufacturer Part Number

MC56F8323EVM

Description

KIT EVALUATION FOR MC56F8323

Manufacturer

Freescale Semiconductor

Type

DSPr

Datasheets

1.CWH-UTP-ONCE-HE.pdf

(2 pages)

2.MC56F8323EVM.pdf

(72 pages)

3.MC56F8323EVME.pdf

(140 pages)

Specifications of MC56F8323EVM

Contents

Module and Misc Hardware

Processor To Be Evaluated

MC56F8322 and MC56F8323

Data Bus Width

16 bit

Interface Type

RS-232

For Use With/related Products

MC56F8322, MC56F8323

Lead Free Status / RoHS Status

Contains lead / RoHS non-compliant

- Current page: 25 of 140

- Download datasheet (742Kb)

Freescale Semiconductor

Preliminary

Signal Name

(GPIOA2)

(GPIOA3)

(GPIOA4)

(MISO1)

(MOSI1)

PWMA2

PWMA3

PWMA4

(SS1)

Table 2-2 Signal and Package Information for the 64-Pin LQFP

Pin No.

7

8

9

Schmitt

Schmitt

Schmitt

Schmitt

Schmitt

Schmitt

Output

Output

Output

Output

Output

Output

Output

Output

Input/

Input/

Input/

Input/

Input/

Type

Input

State During

disabled,

pull-up is

disabled,

pull-up is

disabled,

pull-up is

output is

output is

output is

In reset,

In reset,

In reset,

enabled

enabled

enabled

Reset

56F8323 Technical Data, Rev. 17

PWMA2 — This is one of six PWMA output pins.

SPI 1 Slave Select — SS1 is used in slave mode to indicate to the

SPI module that the current transfer is to be received.

Port A GPIO — This GPIO pin can be individually programmed as

an input or output pin.

In the 56F8323, the default state after reset is PWMA2.

In the 56F8123, the default state is not one of the functions offered

and must be reconfigured.

PWMA3 — This is one of six PWMA output pins.

SPI 1 Master In/Slave Out — This serial data pin is an input to a

master device and an output from a slave device. The MISO line of a

slave device is placed in the high-impedance state if the slave device

is not selected. The slave device places data on the MISO line a

half-cycle before the clock edge the master device uses to latch the

data.

Port A GPIO — This GPIO pin can be individually programmed as

an input or output pin.

In the 56F8323, the default state after reset is PWMA3.

In the 56F8123, the default state is not one of the functions offered

and must be reconfigured.

PWMA4 — This is one of six PWMA output pins.

SPI 1 Master Out/Slave In — This serial data pin is an output from a

master device and an input to a slave device. The master device

places data on the MOSI line a half-cycle before the clock edge the

slave device uses to latch the data.

Port A GPIO — This GPIO pin can be individually programmed as

an input or output pin.

In the 56F8323, the default state after reset is PWMA4.

In the 56F8123, the default state is not one of the functions offered

and must be reconfigured.

Signal Description

Signal Pins

25

Related parts for MC56F8323EVM

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet: