AT91SAM7XC512-CU Atmel, AT91SAM7XC512-CU Datasheet

AT91SAM7XC512-CU

Specifications of AT91SAM7XC512-CU

Available stocks

Related parts for AT91SAM7XC512-CU

AT91SAM7XC512-CU Summary of contents

Page 1

... EmbeddedICE In-circuit Emulation, Debug Communication Channel Support • Internal High-speed Flash – 512 Kbytes (AT91SAM7XC512) Organized in Two Banks of 1024 Pages of 256 Bytes (Dual Plane) – 256 Kbytes (AT91SAM7XC256) Organized in 1024 Pages of 256 Bytes (Single Plane) – 128 Kbytes (AT91SAM7XC128) Organized in 512 Pages of 256 Bytes (Single Plane) • ...

Page 2

... Seventeen Peripheral DMA Controller (PDC) Channels • One Advanced Encryption System (AES) – 256-, 192-, 128-bit Key Algorithm, Compliant with FIPS PUB 197 Specifications (AT91SAM7XC512) – 128-bit Key Algorithm, Compliant with FIPS PUB 197 Specifications (AT91SAM7XC256/128) – Buffer Encryption/Decryption Capabilities with PDC • ...

Page 3

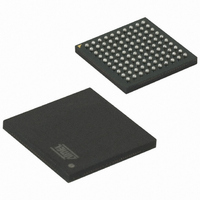

... Fully Static Operation MHz at 1.65V and 85⋅ C Worst Case Conditions • Available in 100-lead LQFP Green and 100-ball TFBGA Green Packages 6209DS–ATARM–17-Feb-09 AT91SAM7XC512/256/128 Preliminary 3 ...

Page 4

... Description Atmel's AT91SAM7XC512/256/128 is a member of a series of highly integrated Flash microcon- trollers based on the 32-bit ARM RISC processor. It features 512/256/128 Kbyte high-speed Flash and 128/64/32 Kbyte SRAM, a large set of peripherals, including an 802.3 Ethernet MAC, a CAN controller, an AES 128 Encryption accelerator and a Triple Data Encryption System. A complete set of system functions minimizes the number of external components ...

Page 5

... AT91SAM7XC512/256/128 Block Diagram Figure 2-1. JTAGSEL IRQ0-IRQ1 PCK0-PCK3 VDDCORE VDDFLASH VDDCORE SPI0_NPCS0 SPI0_NPCS1 SPI0_NPCS2 SPI0_NPCS3 SPI0_MISO SPI0_MOSI SPI0_SPCK SPI1_NPCS0 SPI1_NPCS1 SPI1_NPCS2 SPI1_NPCS3 SPI1_MISO SPI1_MOSI SPI1_SPCK 6209DS–ATARM–17-Feb-09 AT91SAM7XC512/256/128 Preliminary AT91SAM7XC512/256/128 Block Diagram TDI TDO ICE JTAG TMS SCAN TCK System Controller ...

Page 6

... Test Mode Select DRXD Debug Receive Data DTXD Debug Transmit Data IRQ0 - IRQ1 External Interrupt Inputs FIQ Fast Interrupt Input PA0 - PA30 Parallel IO Controller A PB0 - PB30 Parallel IO Controller B AT91SAM7XC512/256/128 Preliminary 6 Active Type Level Power Power Power Power Power Power Power Ground ...

Page 7

... Master Out Slave In SPIx_SPCK SPI Serial Clock SPIx_NPCS0 SPI Peripheral Chip Select 0 SPIx_NPCS1-NPCS3 SPI Peripheral Chip Select TWD Two-wire Serial Data TWCK Two-wire Serial Clock 6209DS–ATARM–17-Feb-09 AT91SAM7XC512/256/128 Preliminary Type USB Device Port Analog Analog USART I/O I/O Input Output Input Input ...

Page 8

... ECRS Carrier Sense ECOL Collision Detected EMDC Management Data Clock EMDIO Management Data Input/Output EF100 Force 100 Mbits/sec. Note: 1. Refer to Section 6. ”I/O Lines AT91SAM7XC512/256/128 Preliminary 8 Type Analog-to-Digital Converter Analog Analog Input Analog Fast Flash Programming Interface Input Input I/O Output Output ...

Page 9

... Package The AT91SAM7XC512/256/128 is available in 100-lead LQFP Green and 100-ball TFBGA RoHS-compliant packages. 4.1 100-lead LQFP Package Outline Figure 4-1 tion is given in the Mechanical Characteristics section of the full datasheet. Figure 4-1. 6209DS–ATARM–17-Feb-09 AT91SAM7XC512/256/128 Preliminary shows the orientation of the 100-lead LQFP package. A detailed mechanical descrip- ...

Page 10

... VDDCORE 40 16 GND 41 17 VDDIO 42 18 PA10/PGMM2 43 19 PA11/PGMM3 44 20 PA12/PGMD0 45 21 PA13/PGMD1 46 22 PA14/PGMD2 47 23 PA15/PGMD3 48 24 PA16/PGMD4 49 25 PA17/PGMD5 50 AT91SAM7XC512/256/128 Preliminary 10 PA18/PGMD6 51 PB9 52 PB8 53 PB14 54 PB13 55 PA23/PGMD11 PB6 56 PA24/PGMD12 GND 57 VDDIO 58 PB5 59 PA25/PGMD13 PB15 60 PA26/PGMD14 PB17 61 VDDCORE 62 VDDCORE PB7 ...

Page 11

... PA16/PGMD4 E4 B10 PA17/PGMD5 E5 C1 PB16 E6 C2 PB4 E7 C3 PB10 E8 C4 PB3 E9 C5 PB0 E10 6209DS–ATARM–17-Feb-09 AT91SAM7XC512/256/128 Preliminary shows the orientation of the 100-ball TFBGA package. A detailed mechanical 100-ball TFBGA Package Orientation (Top View BALL A1 Signal Name Pin Signal Name PB17 F1 ...

Page 12

... Power Consumption The AT91SAM7XC512/256/128 has a static current of less than 60 µA on VDDCORE at 25°C, including the RC oscillator, the voltage regulator and the power-on reset when the brownout detector is deactivated. Activating the brownout detector adds 28 µA static current. ...

Page 13

... For example, two capacitors can be used in parallel: 100 nF NPO and 4.7 µF X7R. 5.4 Typical Powering Schematics The AT91SAM7XC512/256/128 supports a 3.3V single supply mode. The internal regulator input connected to the 3.3V source and its output feeds VDDCORE and the VDDPLL. 1 shows the power schematics to be used for USB bus-powered systems ...

Page 14

... Test Pin AT91SAM7XC512/256/128 when asserted high. The TST pin integrates a permanent pull-down resistor of about 15 kΩ to GND. To eliminate any risk of entering the test mode due to noise on the TST pin, it should be tied to GND if the FFPI is not used, or pulled down with an external low-value resistor (such as 1 kΩ) . ...

Page 15

... The PIO lines PA0 to PA3 are high-drive current capable. Each of these I/O lines can drive permanently. The remaining I/O lines can draw only 8 mA. However, the total current drawn by all the I/O lines cannot exceed 200 mA. 6209DS–ATARM–17-Feb-09 AT91SAM7XC512/256/128 Preliminary 15 ...

Page 16

... Alignment checking of all data accesses – Abort generation in case of misalignment • Remap Command – Remaps the SRAM in place of the embedded non-volatile memory – Allows handling of dynamic exception vectors AT91SAM7XC512/256/128 Preliminary 16 ® high-performance 32-bit instruction set ® high code density 16-bit instruction set Controller 6209DS– ...

Page 17

... Low bus arbitration overhead – One Master Clock cycle needed for a transfer from memory to peripheral – Two Master Clock cycles needed for a transfer from peripheral to memory • Next Pointer management for reducing interrupt latency requirements 6209DS–ATARM–17-Feb-09 AT91SAM7XC512/256/128 Preliminary wait states 17 ...

Page 18

... Full chip erase time – 10,000 write cycles, 10-year data retention capability – 8 lock bits, each protecting 8 sectors of 64 pages – Protection Mode to secure contents of the Flash • 32 Kbytes of Fast SRAM – Single-cycle access at full speed AT91SAM7XC512/256/128 Preliminary 18 6209DS–ATARM–17-Feb-09 ...

Page 19

... Figure 8-1. AT91SAM7XC512/256/128 Memory Mapping Address Memory Space 0x0000 0000 Internal Memories 256 MBytes 0x0FFF FFFF 0x1000 0000 Undefined 14 x 256 MBytes (Abort) 3,584 MBytes 0xEFFF FFFF 0xF000 0000 Internal Peripherals 256 MBytes 0xFFFF FFFF 6209DS–ATARM–17-Feb-09 AT91SAM7XC512/256/128 Preliminary Internal Memory Mapping ...

Page 20

... After reset and until the Remap Command is performed, the SRAM is only accessible at address 0x0020 0000. After Remap, the SRAM also becomes available at address 0x0. 8.4.2 Internal ROM The AT91SAM7XC512/256/128 embeds an Internal ROM. At any time, the ROM is mapped at address 0x30 0000. The ROM contains the FFPI and the SAM-BA program. 8.4.3 Internal Flash • ...

Page 21

... Embedded Flash 8.5.1 Flash Overview • The Flash of the AT91SAM7XC512 is organized in two banks (dual plane) 0f 1254 pages of 256 bytes. The 524, 288 bytes are organized in 32-bit words. • The Flash of the AT91SAM7XC256 is organized in 1024 pages of 256 bytes (single plane). It reads as 65,536 32-bit words. ...

Page 22

... Asserting the ERASE pin clears the lock bits, thus unlocking the entire Flash. 8.5.4 Security Bit Feature The AT91SAM7XC512/256/128 features a security bit, based on a specific NVM-Bit. When the security is enabled, any access to the Flash, either through the ICE interface or through the Fast AT91SAM7XC512/256/128 Preliminary 22 6209DS– ...

Page 23

... The SAM-BA Boot Assistant is a default Boot Program that provides an easy way to program in- situ the on-chip Flash memory. The SAM-BA Boot Assistant supports serial communication via the DBGU or the USB Device Port. • Communication via the DBGU supports a wide range of crystals from MHz via software auto-detection. 6209DS–ATARM–17-Feb-09 AT91SAM7XC512/256/128 Preliminary 23 ...

Page 24

... The SAM-BA Boot is in ROM and is mapped at address 0x0 when the GPNVM Bit 2 is set to 0. When GPNVM bit 2 is set to 1, the device boots from the Flash. When GPNVM bit 2 is set to 0, the device boots from ROM (SAM-BA). AT91SAM7XC512/256/128 Preliminary 24 6209DS–ATARM–17-Feb-09 ...

Page 25

... Figure 9-1 on page 26 Figure 8-1 on page 19 erals. Note that the Memory Controller configuration user interface is also mapped within this address space. 6209DS–ATARM–17-Feb-09 AT91SAM7XC512/256/128 Preliminary shows the System Controller Block Diagram. shows the mapping of the User Interface of the System Controller periph- 25 ...

Page 26

... Figure 9-1. NRST XIN XOUT PLLRC PA0-PA30 PB0-PB30 AT91SAM7XC512/256/128 Preliminary 26 System Controller Block Diagram System Controller irq0-irq1 Advanced fiq Interrupt Controller periph_irq[2..19] pit_irq rtt_irq wdt_irq dbgu_irq pmc_irq rstc_irq efc_irq MCK Debug periph_nreset Unit dbgu_rxd Periodic MCK debug Interval periph_nreset Timer SLCK ...

Page 27

... Brownout Detector and Power-on Reset The AT91SAM7XC512/256/128 embeds one brownout detection circuit and a power-on reset cell. The power-on reset is supplied with and monitors VDDCORE. Both signals are provided to the Flash to prevent any code corruption during power-up or power- down sequences or if brownouts occur on the power supplies. ...

Page 28

... RC Oscillator ranges between 22 KHz and 42 KHz • Main Oscillator frequency ranges between 3 and 20 MHz • Main Oscillator can be bypassed • PLL output ranges between 80 and 200 MHz It provides SLCK, MAINCK and PLLCK. Figure 9-2. AT91SAM7XC512/256/128 Preliminary 28 Clock Generator Block Diagram Clock Generator Embedded RC ...

Page 29

... Programmable positive/negative edge-triggered or high/low level-sensitive external • 8-level Priority Controller – Drives the normal interrupt nIRQ of the processor – Handles priority of the interrupt sources 6209DS–ATARM–17-Feb-09 AT91SAM7XC512/256/128 Preliminary Power Management Controller Block Diagram Master Clock Controller SLCK Prescaler MAINCK /1,/2,/4, ...

Page 30

... Offers visibility of COMMRX and COMMTX signals from the ARM Processor • Chip ID Registers – Identification of the device revision, sizes of the embedded memories, set of – Chip ID is 0x271C 0A40 (VERSION 0) for AT91SAM7XC512 – Chip ID is 0x271B 0940 (VERSION 0) for AT91SAM7XC256 – Chip ID is 0x271A 0740 (VERSION 0) for AT91SAM7XC128 9 ...

Page 31

... Synchronous output, provides Set and Clear of several I/O lines in a single write 9.10 Voltage Regulator Controller The purpose of this controller is to select the Power Mode of the Voltage Regulator between Normal Mode (bit 0 is cleared) or Standby Mode (bit 0 is set). 6209DS–ATARM–17-Feb-09 AT91SAM7XC512/256/128 Preliminary 31 ...

Page 32

... FFFF. Each peripheral is allocated 16 Kbytes of address space. A complete memory map is provided in 10.2 Peripheral Identifiers The AT91SAM7XC512/256/128 embeds a wide range of peripherals. Peripheral Identifiers of the AT91SAM7XC512/256/128. Unique peripheral identifiers are defined for both the Advanced Interrupt Controller and the Power Management Controller. Table 10-1. Peripheral ID 0 ...

Page 33

... Peripheral Multiplexing on PIO Lines The AT91SAM7XC512/256/128 features two PIO controllers, PIOA and PIOB, that multiplex the I/O lines of the peripheral set. Each PIO Controller controls 31 lines. Each line can be assigned to one of two peripheral func- tions Some of them can also be multiplexed with the analog inputs of the ADC Controller ...

Page 34

... CANRX PA20 CANTX PA21 TF PA22 TK PA23 TD PA24 RD PA25 RK PA26 RF PA27 DRXD PA28 DTXD PA29 FIQ PA30 IRQ0 AT91SAM7XC512/256/128 Preliminary 34 Peripheral B Comments High-Drive High-Drive SPI1_NPCS1 High-Drive SPI1_NPCS2 High-Drive SPI1_NPCS3 SPI0_NPCS1 SPI0_NPCS2 SPI0_NPCS3 PCK1 IRQ1 TCLK2 SPI1_NPCS0 SPI1_SPCK SPI1_MOSI SPI1_MISO SPI1_NPCS1 SPI1_NPCS2 PCK3 ...

Page 35

... PB22 PWM3 PB23 TIOA0 PB24 TIOB0 PB25 TIOA1 PB26 TIOB1 PB27 TIOA2 PB28 TIOB2 PB29 PCK1 PB30 PCK2 6209DS–ATARM–17-Feb-09 AT91SAM7XC512/256/128 Preliminary Peripheral B Comments PCK0 SPI1_NPCS1 SPI1_NPCS2 TCLK0 SPI0_NPCS1 SPI0_NPCS2 SPI1_NPCS3 SPI0_NPCS3 ADTRG TCLK1 PCK0 PCK1 PCK2 DCD1 DSR1 DTR1 ...

Page 36

... Programmable phase and polarity per chip select – Programmable transfer delays per chip select, between consecutive transfers and – Programmable delay between consecutive transfers – Selectable mode fault detection – Maximum frequency Master Clock AT91SAM7XC512/256/128 Preliminary 36 peripherals Sensors between clock and data ® ...

Page 37

... Receiver and transmitter can be programmed to start automatically or on detection of different event on the frame sync signal • Receiver and transmitter include a data signal, a clock signal and a frame synchronization signal 6209DS–ATARM–17-Feb-09 AT91SAM7XC512/256/128 Preliminary 2 C compatible devices (refer to the TWI section of the datasheet) 37 ...

Page 38

... Independent enable/disable commands – Independent clock selection – Independent period and duty cycle, with double buffering – Programmable selection of the output waveform polarity – Programmable center or left aligned output waveform AT91SAM7XC512/256/128 Preliminary 38 Table 10-4 Timer Counter Clocks Assignment Clock MCK/2 ...

Page 39

... Data, remote, error and overload frame handling 10.15 128-bit Advanced Encryption Standard • Compliant with FIPS Publication 197, Advanced Encryption Standard (AES) • 128-bit (AT91SAM7XC256/128) or 128-bit/192-bit/256-bit (AT91SAM7XC512) Cryptographic Key • 12-clock Cycles Encryption/Decryption Processing Time (AT91SAM7XC256/128) • 12/13/14-clock Cycles Encryption/Decryption Processing Time (AT91SAM7XC512) • ...

Page 40

... External voltage reference for better accuracy on low voltage inputs • Individual enable and disable of each channel • Multiple trigger sources – Hardware or software trigger – External trigger pin – Timer Counter outputs TIOA0 to TIOA2 trigger • Sleep Mode and conversion sequencer AT91SAM7XC512/256/128 Preliminary 40 6209DS–ATARM–17-Feb-09 ...

Page 41

... Automatic wakeup on trigger and back to sleep mode after conversions of all • Four of eight analog inputs shared with digital signals 6209DS–ATARM–17-Feb-09 AT91SAM7XC512/256/128 Preliminary enabled channels 41 ...

Page 42

... Package Drawings Figure 11-1. LQFP Package Drawing AT91SAM7XC512/256/128 Preliminary 42 6209DS–ATARM–17-Feb-09 ...

Page 43

... θ1 θ2 θ aaa bbb ccc ddd 6209DS–ATARM–17-Feb-09 AT91SAM7XC512/256/128 Preliminary 100-lead LQFP Package Dimensions Millimeter Min Nom Max 1.60 0.05 0.15 1.35 1.40 1.45 16.00 BSC 14.00 BSC 16.00 BSC 14.00 BSC 0.08 0.20 0.08 0⋅ 3.5⋅ 7⋅ ...

Page 44

... Figure 11-2. 100-TFBGA Package Drawing All dimensions are in mm AT91SAM7XC512/256/128 Preliminary 44 6209DS–ATARM–17-Feb-09 ...

Page 45

... AT91SAM7XC512/256/128 Ordering Information Table 12-1. Ordering Information MLR A Ordering Code MLR B Ordering Code AT91SAM7XC512-AU AT91SAM7XC512-CU AT91SAM7XC256-AU AT91SAM7XC256B-AU AT91SAM7XC256-CU AT91SAM7XC256B-CU AT91SAM7XC128-AU AT91SAM7XC128B-AU AT91SAM7XC128-CU AT91SAM7XC128B-CU 13. Export Regulations Statement These commodities, technology or software will be exported from France and the applicable Export Administration Regulations will apply. French, United States and other relevant laws, reg- ulations and requirements regarding the export of products may restrict sale, export and re- export of these products ...

Page 46

... Revision History Table 13-1. Revision History Doc. Rev Comments First issue - Unqualified on Intranet 6209S Legal page updated.Qualified on Intranet Added AT91SAM7XC512 to product Reformatted Memories Reordered sub sections in Peripherals Consolidated Memory Mapping in Added package drawings 6209BS Consolidated Memory Mapping in Added TFBGA information page 10 and “ ...

Page 47

... Disclaimer: The information in this document is provided in connection with Atmel products. No license, express or implied, by estoppel or otherwise, to any intellectual property right is granted by this document or in connection with the sale of Atmel products. EXCEPT AS SET FORTH IN ATMEL’S TERMS AND CONDI- TIONS OF SALE LOCATED ON ATMEL’S WEB SITE, ATMEL ASSUMES NO LIABILITY WHATSOEVER AND DISCLAIMS ANY EXPRESS, IMPLIED OR STATUTORY WARRANTY RELATING TO ITS PRODUCTS INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTY OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT ...