HD64F3687GFPV Renesas Electronics America, HD64F3687GFPV Datasheet - Page 188

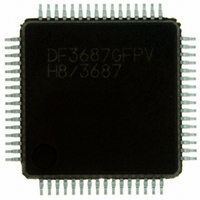

HD64F3687GFPV

Manufacturer Part Number

HD64F3687GFPV

Description

IC H8 MCU FLASH 56K 64LQFP

Manufacturer

Renesas Electronics America

Series

H8® H8/300H Tinyr

Specifications of HD64F3687GFPV

Core Processor

H8/300H

Core Size

16-Bit

Speed

20MHz

Connectivity

I²C, SCI

Peripherals

LVD, POR, PWM, WDT

Number Of I /o

45

Program Memory Size

56KB (56K x 8)

Program Memory Type

FLASH

Ram Size

4K x 8

Voltage - Supply (vcc/vdd)

3 V ~ 5.5 V

Data Converters

A/D 8x10b

Oscillator Type

Internal

Operating Temperature

-20°C ~ 75°C

Package / Case

64-LQFP

Package

64LQFP

Family Name

H8

Maximum Speed

20 MHz

Operating Supply Voltage

3.3|5 V

Data Bus Width

16|32 Bit

Number Of Programmable I/os

45

Interface Type

I2C/SCI

On-chip Adc

8-chx10-bit

Number Of Timers

3

For Use With

R0K436079S000BE - KIT DEV FOR H8/36079 W/COMPILER

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Eeprom Size

-

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

HD64F3687GFPV

Manufacturer:

Renesas Electronics America

Quantity:

10 000

- Current page: 188 of 277

- Download datasheet (2Mb)

Section 2 Instruction Descriptions

2.2.55 (3) SHLL (L)

SHLL (SHift Logical Left)

Operation

ERd (left logical shift)

Assembly-Language Format

SHLL.L ERd

Operand Size

Longword

Description

This instruction shifts the bits in a 32-bit register ERd (destination operand) one bit to the left. The

most significant bit shifts into the carry flag. The least significant bit (bit 0) is cleared to 0.

Available Registers

ERd: ER0 to ER7

Operand Format and Number of States Required for Execution

Notes

The SHLL instruction differs from the SHAL instruction in its effect on the overflow flag.

Rev. 3.00 Dec 13, 2004 page 172 of 258

REJ09B0213-0300

Register direct

Addressing

Mode

Mnemonic

SHLL.L

C

ERd

MSB

Operands

b

31

ERd

1st byte

. . . . . .

1

0

Condition Code

H: Previous value remains unchanged.

N: Set to 1 if the result is negative; otherwise

Z: Set to 1 if the result is zero; otherwise

V: Always cleared to 0.

C: Receives the previous value in bit 31.

2nd byte

3

cleared to 0.

cleared to 0.

Instruction Format

— —

I

0 erd

UI

— —

H

3rd byte

LSB

b

0

U

N

0

4th byte

Z

Shift Logical

V

0

States

No. of

C

2

Related parts for HD64F3687GFPV

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

KIT STARTER FOR M16C/29

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/2D

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

R0K33062P STARTER KIT

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/23 E8A

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/25

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER H8S2456 SHARPE DSPLY

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C38C

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C35C

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8CL3AC+LCD APPS

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR RX610

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R32C/118

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT DEV RSK-R8C/26-29

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR SH7124

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR H8SX/1622

Manufacturer:

Renesas Electronics America

Datasheet: