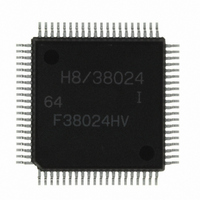

HD64F38024DV Renesas Electronics America, HD64F38024DV Datasheet

HD64F38024DV

Specifications of HD64F38024DV

Available stocks

Related parts for HD64F38024DV

HD64F38024DV Summary of contents

Page 1

To our customers, Old Company Name in Catalogs and Other Documents st On April 1 , 2010, NEC Electronics Corporation merged with Renesas Technology Corporation, and Renesas Electronics Corporation took over all the business of both companies. Therefore, although the ...

Page 2

All information included in this document is current as of the date this document is issued. Such information, however, is subject to change without any prior notice. Before purchasing or using any Renesas Electronics products listed herein, please confirm ...

Page 3

H8/300L Series 16 Software Manual Renesas 16-Bit Single-Chip Microcomputer H8 Family/H8/300L Series The revision list can be viewed directly by clicking the title page. The revision list summarizes the locations of revisions and additions. Details should always be checked by ...

Page 4

Keep safety first in your circuit designs! 1. Renesas Technology Corp. puts the maximum effort into making semiconductor products better and more reliable, but there is always the possibility that trouble may occur with them. Trouble with semiconductors may lead ...

Page 5

General Precautions on Handling of Product 1. Treatment of NC Pins Note: Do not connect anything to the NC pins. The NC (not connected) pins are either not connected to any of the internal circuitry or are used as test ...

Page 6

Rev. 2.00 Dec 27, 2004 page iv of xii ...

Page 7

The H8/300L Series of single-chip microcomputers is built around the high-speed H8/300L CPU, with an architecture featuring eight 16-bit (or sixteen 8-bit) general registers and a concise, optimized instruction set. This manual gives detailed descriptions of the H8/300L instructions. The ...

Page 8

Rev. 2.00 Dec 27, 2004 page vi of xii ...

Page 9

Main Revisions for this Edition Item Page All Revision (See Manual for Details) All references to Hitachi, Hitachi, Ltd., Hitachi Semiconductors, and other Hitachi brand names changed to Renesas Technology Corp. Designation for categories changed from “series” to “group” Rev. ...

Page 10

Rev. 2.00 Dec 27, 2004 page viii of xii ...

Page 11

Section 1 CPU .................................................................................................................... 1.1 Overview........................................................................................................................... 1.1.1 Features ............................................................................................................. 1.1.2 Data Structure ................................................................................................... 1.1.3 Address Space................................................................................................... 1.1.4 Register Configuration...................................................................................... 1.2 Registers............................................................................................................................ 1.2.1 General Registers .............................................................................................. 1.2.2 Control Registers .............................................................................................. 1.2.3 Initial Register Values....................................................................................... 1.3 Instructions........................................................................................................................ 1.3.1 Types of Instructions......................................................................................... 1.3.2 ...

Page 12

BSR (branch to subroutine) ............................................................................. 56 2.2.19 BST (bit store) ................................................................................................. 57 2.2.20 BTST (bit test) ................................................................................................. 58 2.2.21 BXOR (bit exclusive OR)................................................................................ 59 2.2.22 (1) CMP (compare) (byte)CMP ............................................................................ 60 2.2.22 (2) CMP (compare) (word)CMP........................................................................... 61 2.2.23 DAA ...

Page 13

SUB (subtract binary) (byte)SUB ................................................................... 99 2.2.53 (2) SUB (subtract binary) (word)SUB.................................................................. 100 2.2.54 SUBS (subtract with sign extension)............................................................... 101 2.2.55 SUBX (subtract with extend carry) ................................................................. 102 2.2.56 XOR (exclusive OR logical) ........................................................................... 103 2.2.57 XORC (exclusive ...

Page 14

Rev. 2.00 Dec 27, 2004 page xii of xii ...

Page 15

Overview The H8/300L CPU at the heart of the H8/300L Series features 16 general registers of 8 bits each (or 8 registers of 16-bits each), and a concise, optimized instruction set geared to high-speed operation. 1.1.1 Features The H8/300L ...

Page 16

Section 1 CPU Low-power operation Transition to power-down state using SLEEP instruction 1.1.2 Data Structure The H8/300L CPU can process 1-bit data, 4-bit (packed BCD) data, 8-bit (byte) data, and 16-bit (word) data. Bit manipulation instructions operate on 1-bit data ...

Page 17

Data Structure in General Registers: Data of all the sizes above can be stored in general registers as shown in figure 1-1. Data type 1-Bit data 1-Bit data Byte data Byte data Word data 4-Bit BCD data 4-Bit BCD data ...

Page 18

Section 1 CPU Data Structure in Memory: Figure 1-2 shows the structure of data in memory. The H8/300L CPU is able to access word data in memory (MOV.W instruction), but only if the word data starts from an even-numbered address. ...

Page 19

Address Space The H8/300L CPU supports a 64-kbyte address space (program code + data). The memory map differs depending on the particular chip in the H8/300L Series and its operating mode. See the applicable hardware manual for details. 1.1.4 ...

Page 20

Section 1 CPU 1.2 Registers 1.2.1 General Registers All the general registers can be used as both data registers and address registers. When used as address registers, the general registers are accessed as 16-bit registers (R0 to R7). When used ...

Page 21

Bit 7 I Initial value * Read/Write R/W * Not fixed Bit 7—Interrupt Mask Bit (I): When this bit is set to 1, all interrupts except NMI are masked. This bit is set to 1 automatically at the start of ...

Page 22

Section 1 CPU The initial value of the stack pointer (R7) is not fixed. To prevent program crashes the stack pointer should be initialized by software, by the first instruction executed after a reset. 1.3 Instructions Features: The H8/300L CPU ...

Page 23

Instruction Functions Tables 1-2 to 1-9 give brief descriptions of the instructions in each functional group. The following notation is used. Notation Rd General register (destination) Rs General register (source) Rn General register (EAd) Destination operand (EAs) Source operand ...

Page 24

Section 1 CPU Table 1-2 Data Transfer Instructions Instruction Size* B/W MOV W POP W PUSH * Size: Operand size B: Byte W: Word Rev. 2.00 Dec 27, 2004 page 10 of 128 REJ09B0214-0200 Function (EAs) Rd, Rs (EAd) Moves ...

Page 25

Table 1-3 Arithmetic Instructions Instruction Size* B/W ADD SUB B ADDX SUBX B INC DEC W ADDS SUBS B DAA DAS B MULXU B DIVXU B/W CMP B NEG * Size: Operand size B: Byte W: Word Function Rd ± ...

Page 26

Section 1 CPU Table 1-4 Logic Operation Instructions Instruction Size* B AND XOR B NOT * Size: Operand size B: Byte Table 1-5 Shift Instructions Instruction Size* B SHAL SHAR B SHLL SHLR B ROTL ROTR B ...

Page 27

Table 1-6 Bit Manipulation Instructions Instruction Size* B BSET B BCLR B BNOT B BTST B BAND B BIAND B BOR B BIOR Function 1 (<bit-No.> of <EAd>) Sets a specified bit in a general register or memory to 1. ...

Page 28

Section 1 CPU Table 1-6 Bit Manipulation Instructions (Cont.) Instruction Size* B BXOR B BIXOR B BLD B BILD B BST B BIST * Size: Operand size B: Byte Rev. 2.00 Dec 27, 2004 page 14 of 128 REJ09B0214-0200 Function ...

Page 29

Table 1-7 Branching Instructions Instruction Size* Bcc JMP BSR JSR RTS Function Branches if condition cc is true. The branching conditions are as follows. Mnemonic Description Always (True) BRA (BT) Never (False) BRN (BF) High BHI Low or Same BLS ...

Page 30

Section 1 CPU Table 1-8 System Control Instructions Instruction Size* RTE SLEEP B LDC B STC B ANDC B ORC B XORC NOP * Size: Operand size B: Byte Rev. 2.00 Dec 27, 2004 page 16 of 128 REJ09B0214-0200 Function ...

Page 31

Table 1-9 Block Data Transfer Instruction Instruction Size* EEPMOV Notes on Bit Manipulation Instructions: BSET, BCLR, BNOT, BST, and BIST are read- modify-write instructions. They read a byte of data, modify one bit in the byte, then write the byte ...

Page 32

Section 1 CPU Before Execution of BCLR Instruction Input/output Input Input Pin state Low High PCR4 0 0 PDR4 1 0 Execution of BCLR Instruction ;clear bit 0 in PCR4 BCLR #0 @PCR4 After Execution of BCLR ...

Page 33

Before Execution of BSET Instruction Input/output Input Input Pin state Low High PCR4 0 0 PDR4 1 0 Execution of BSET Instruction ;set bit 0 in port 4 port data register BSET #0 @PDR4 After Execution of ...

Page 34

Section 1 CPU 1.3.3 Basic Instruction Formats (1) Format of Data Transfer Instructions Figure 1-5 shows the format used for data transfer instructions disp ...

Page 35

Format of Arithmetic, Logic Operation, and Shift Instructions Figure 1-6 shows the format used for arithmetic, logic operation, and shift instructions ...

Page 36

Section 1 CPU (3) Format of Bit Manipulation Instructions Figure 1-7 shows the format used for bit manipulation instructions ...

Page 37

Notation op: Operation field Register field abs.: Absolute address IMM: Immediate data Figure 1-7 Instruction Format of Bit Manipulation Instructions ...

Page 38

Section 1 CPU (4) Format of Branching Instructions Figure 1-8 shows the format used for branching instructions Notation op: Operation field cc: Condition field ...

Page 39

Format of System Control Instructions Figure 1-9 shows the format used for system control instructions Notation op: Operation field Register field IMM: Immediate data Figure 1-9 Instruction ...

Page 40

Section 1 CPU 1.3.4 Addressing Modes and Effective Address Calculation Table 1-10 lists the eight addressing modes and their assembly-language notation. Each instruction can use a specific subset of these addressing modes. Arithmetic, logic, and shift instructions use register direct ...

Page 41

Register Indirect with Displacement—@(d:16, Rn): This mode, which is used only in MOV instructions, is similar to register indirect but the instruction has a second word (bytes 3 and 4) which is added to the contents of the specified ...

Page 42

Section 1 CPU If an odd address is specified as a branch destination or as the operand address of a MOV.W instruction, the least significant bit is regarded as 0, causing word access to be performed at the address preceding ...

Page 43

Table 1-11 Effective Address Calculation (2) Addr essing mode, No. instruction format 3 Register indirect with displacement @(d:16, Rn reg OP disp 4 Register indirect with pre-decrement @- reg OP ...

Page 44

Section 1 CPU Table 1-11 Effective Address Calculation (3) Addr essing mode , No. instruction format 6 Immediate #xx: IMM OP Immediate #xx: IMM 7 PC-relative @(d:8, PC disp OP 8 Memory ...

Page 45

Section 2 Instruction Set 2.1 Explanation Format Section 2 gives full descriptions of all the H8/300L Series instructions, presenting them in alphabetic order. Each instruction is explained in a table like the following: ADD (add binary) (byte) Operation Rd + ...

Page 46

Section 2 Instruction Set The parts of the table are explained below. Name: The full and mnemonic names of the instruction are given at the top of the page. Operation: The instruction is described in symbolic notation. The following symbols ...

Page 47

The operand size is indicated by the letter B (byte (word). Some instructions have restrictions on the size of operands they handle. The abbreviation EAs or EAd (effective address of source or destination) is used for operands that ...

Page 48

Section 2 Instruction Set Instruction Formats: Each possible format of the instruction is shown explicitly, indicating the addressing mode, the object code, and the number of states required for execution when the instruction and its operands are located in on-chip ...

Page 49

BSET R1L, R2H R1L don't care R2H Bit 3 is set to 1 BLD #5, @H'FF02:8 Bit No H'FF02 Loaded to C (carry) ...

Page 50

Section 2 Instruction Set 2.2 Instructions 2.2.1 (1) ADD (add binary) (byte) ADD Operation Rd + (EAs) Rd Assembly-Language Format ADD.B <EAs>, Rd Operand Size Byte Description This instruction adds the source operand to the contents of an 8-bit general ...

Page 51

ADD (add binary) (word) Operation Assembly-Language Format ADD.W Rs, Rd Operand Size Word Description This instruction adds word data in two general registers and places the result in the second general register. Instruction Formats ...

Page 52

Section 2 Instruction Set 2.2.2 ADDS (add with sign extension) Operation Assembly-Language Format ADDS #1, Rd ADDS #2, Rd Operand Size Word Description This instruction adds the immediate value ...

Page 53

ADDX (add with extend carry) Operation Rd + (EAs Assembly-Language Format ADDX <EAs>, Rd Operand Size Byte Description This instruction adds the source operand and carry flag to the contents of an 8-bit general register and ...

Page 54

Section 2 Instruction Set 2.2.4 AND (AND logical) Operation Rd (EAs) Rd Assembly-Language Format AND <EAs>, Rd Operand Size Byte Description This instruction ANDs the source operand with the contents of an 8-bit general register and places the result in ...

Page 55

ANDC (AND control register) Operation CCR #IM CCR Assembly-Language Format ANDC #xx:8, CCR Operand Size Byte Description This instruction ANDs the condition code register (CCR) with immediate data and places the result in the condition code register. Bits 6 ...

Page 56

Section 2 Instruction Set 2.2.6 BAND (bit AND) Operation C (<Bit No.> of <EAd>) Assembly-Language Format BAND #xx:3, <EAd> Operand Size Byte Description This instruction ANDs a specified bit with the carry flag and places the result in the carry ...

Page 57

Bcc (branch conditionally) Operation If cc then PC + d:8 PC else next; Assembly-Language Format d Condition code field (For mnemonics, see the table on the next page.) Operand Size Condition Code I H — — — ...

Page 58

Section 2 Instruction Set Bcc (branch conditionally) Description If the specified condition is false, this instruction does nothing; the next instruction is executed. If the specified condition is true, a signed displacement is added to the address of the next ...

Page 59

Bcc (branch conditionally) Instruction Formats and Number of Execution States Adressing mode Mnem. PC relative BRA (BT) PC relative BRN (BF) PC relative BHI PC relative BLS PC relative BCC (BHS) PC relative BCS (BLO) PC relative BNE PC relative ...

Page 60

Section 2 Instruction Set 2.2.8 BCLR (bit clear) Operation 0 (<Bit No.> of <EAd>) Assembly-Language Format BCLR #xx:3, <EAd> BCLR Rn, <EAd> Operand Size Byte Description This instruction clears a specified bit in the destination operand to 0. The bit ...

Page 61

BIAND (bit invert AND) Operation C [ ¬ (<Bit No.> of <EAd>)] Assembly-Language Format BIAND #xx:3, <EAd> Operand Size Byte Description This instruction ANDs the inverse of a specified bit with the carry flag and places the result in ...

Page 62

Section 2 Instruction Set 2.2.10 BILD (bit invert load) Operation ¬ (<Bit No.> of <EAd>) C Assembly-Language Format BILD #xx:3, <EAd> Operand Size Byte Description This instruction loads the inverse of a specified bit into the carry flag. The specified ...

Page 63

BIOR (bit invert inclusive OR) Operation C [¬ (<Bit No.> of <EAd>)] Assembly-Language Format BIOR #xx:3, <EAd> Operand Size Byte Description This instruction ORs the inverse of a specified bit with the carry flag and places the result in ...

Page 64

Section 2 Instruction Set 2.2.12 BIST (bit invert store) Operation ¬ C (<Bit No.> of <EAd>) Assembly-Language Format BIST #xx:3, <EAd> Operand Size Byte Description This instruction stores the inverse of the carry flag to a specified bit location in ...

Page 65

BIXOR (bit invert exclusive OR) Operation C [¬ (<Bit No.> of <EAd>)] Assembly-Language Format BIXOR #xx:3, <EAd> Operand Size Byte Description This instruction exclusive-ORs the inverse of a specified bit with the carry flag and places the result in ...

Page 66

Section 2 Instruction Set 2.2.14 BLD (bit load) Operation (<Bit No.> of <EAd>) C Assembly-Language Format BLD #xx:3, <EAd> Operand Size Byte Description This instruction loads a specified bit into the carry flag. The specified bit can be located in ...

Page 67

BNOT (bit NOT) Operation ¬ (<Bit No.> of <EAd>) (<Bit No.> of <EAd>) Assembly-Language Format BNOT #xx:3, <EAd> BNOT Rn, <EAd> Operand Size Byte Description This instruction inverts a specified bit in a general register or memory location. The ...

Page 68

Section 2 Instruction Set 2.2.16 BOR (bit inclusive OR) Operation C (<Bit No.> of <EAd>) Assembly-Language Format BOR #xx:3, <EAd> Operand Size Byte Description This instruction ORs a specified bit with the carry flag and places the result in the ...

Page 69

BSET (bit set) Operation 1 (<Bit No.> of <EAd>) Assembly-Language Format BSET #xx:3,<EAd> BSET Rn,<EAd> Operand Size Byte Description This instruction sets a specified bit in the destination operand to 1. The bit number can be specified by 3-bit ...

Page 70

Section 2 Instruction Set 2.2.18 BSR (branch to subroutine) Operation PC @– d:8 PC Assembly-Language Format BSR d:8 Operand Size — Description This instruction pushes the program counter (PC) value onto the stack, then adds a specified displacement ...

Page 71

BST (bit store) Operation C (<Bit No.> of <EAd>) Assembly-Language Format BST #xx:3, <EAd> Operand Size Byte Description This instruction stores the carry flag to a specified flag location in a general register or memory. The bit number is ...

Page 72

Section 2 Instruction Set 2.2.20 BTST (bit test) Operation ¬ (<Bit No.> of <EAd>) Z Assembly-Language Format BTST #xx:3, <EAd> BTST Rn, <EAd> Operand Size Byte Description This instruction tests a specified bit in a general register or memory location ...

Page 73

BXOR (bit exclusive OR) Operation C (<Bit No.> of <EAd>) Assembly-Language Format BXOR #xx:3, <EAd> Operand Size Byte Description This instruction exclusive-ORs a specified bit with the carry flag and places the result in the carry flag. The specified ...

Page 74

Section 2 Instruction Set 2.2.22 (1) CMP (compare) (byte) Operation Rd – (EAs); set condition code Assembly-Language Format CMP.B <EAs>, Rd Operand Size Byte Description This instruction subtracts an 8-bit source register or immediate data from an 8-bit destination register ...

Page 75

CMP (compare) (word) Operation Rd – Rs; set condition code Assembly-Language Format CMP.W Rs, Rd Operand Size Word Description This instruction subtracts a source register from a destination register and sets the condition code flags according to the ...

Page 76

Section 2 Instruction Set 2.2.23 DAA (decimal adjust add) Operation Rd (decimal adjust) Rd Assembly-Language Format DAA Rd Operand Size Byte Description When the result of an addition operation performed by the ADD.B or ADDX instruction on 4-bit BCD data ...

Page 77

DAA (decimal adjust add) Instruction Formats and Number of Execution States Addressing Mnem. Operands mode Register direct DAA Instruction code 1st byte 2nd byte Rev. 2.00 Dec 27, 2004 page 63 of 128 Section 2 ...

Page 78

Section 2 Instruction Set 2.2.24 DAS (decimal adjust subtract) Operation Rd (decimal adjust) Rd Assembly-Language Format DAS Rd Operand Size Byte Description When the result of a subtraction operation performed by the SUB.B, SUBX, or NEG instruction on 4-bit BCD ...

Page 79

DEC (decrement) Operation Rd – Assembly-Language Format DEC Rd Operand Size Byte Description This instruction decrements an 8-bit general register and places the result in the general register. Instruction Formats and Number of Execution States Addressing Mnem. ...

Page 80

Section 2 Instruction Set 2.2.26 DIVXU (divide extend as unsigned) Operation Rd ÷ Assembly-Language Format DIVXU Rs, Rd Operand Size Byte Description This instruction divides a 16-bit general register by an 8-bit general register and places the result ...

Page 81

DIVXU (divide extend as unsigned) Note: DIVXU Overflow Since the DIVXU instruction performs 16-bit ÷ 8-bit divisor byte is equal to or less than the upper byte of the dividend. For example, H'FFFF ÷ H'01 H'FFFF causes an overflow. (The ...

Page 82

Section 2 Instruction Set 2.2.27 EEPMOV (move data to EEPROM) Operation if R4L 0 then repeat @R5+ @R6+ R4L – 1 R4L until R4L = 0 else next; Assembly-Language Format EEPMOV Operand Size — Description This instruction moves a block ...

Page 83

INC (increment) Operation Assembly-Language Format INC Rd Operand Size Byte Description This instruction increments an 8-bit general register and places the result in the general register. Instruction Formats and Number of Execution States Addressing Mnem. ...

Page 84

Section 2 Instruction Set 2.2.29 JMP (jump) Operation (EAd) PC Assembly-Language Format JMP <EA> Operand Size — Description This instruction branches unconditionally to a specified destination address. The destination address must be even. Instruction Formats and Number of Execution States ...

Page 85

JSR (Jump to subroutine) Operation PC @-SP (EAd) PC Assembly-Language Format JSR <EA> Operand Size — Description This instruction pushes the program counter onto the stack, then branches to a specified destination address. The program counter value pushed on ...

Page 86

Section 2 Instruction Set 2.2.31 LDC (load to control register) LDC Operation (EAs) CCR Assembly-Language Format LDC <EAs>, CCR Operand Size Byte Description This instruction loads the source operand contents into the condition code register (CCR). Bits 4 and 6 ...

Page 87

MOV (move data) (byte) Operation Rs Rd Assembly-Language Format MOV.B Rs, Rd Operand Size Byte Description This instruction moves one byte of data from a source register to a destination register and sets condition code flags according to ...

Page 88

Section 2 Instruction Set 2.2.32 (2) MOV (move data) (word) Operation Rs Rd Assembly-Language Format MOV.W Rs, Rd Operand Size Word Description This instruction moves one word of data from a source register to a destination register and sets condition ...

Page 89

MOV (move data) (byte) Operation (EAs) Rd Assembly-Language Format MOV.B <EAs>, Rd Operand Size Byte Description This instruction moves one byte of data from a source operand to a destination register and sets condition code flags according to ...

Page 90

Section 2 Instruction Set 2.2.32 (4) MOV (move data) (word) Operation (EAs) Rd Assembly-Language Format MOV.W <EAs>, Rd Operand Size Word Description This instruction moves one word of data from a source operand to a destination register and sets condition ...

Page 91

MOV (move data) (byte) Operation Rs (EAd) Assembly-Language Format MOV.B Rs, <EAd> Operand Size Byte Description This instruction moves one byte of data from a source register to memory and sets condition code flags according to the data ...

Page 92

Section 2 Instruction Set 2.2.32 (6) MOV (move data) (word) Operation Rs (EAd) Assembly-Language Format MOV.W Rs, <EAd> Operand Size Word Description This instruction moves one word of data from a general register to memory and sets condition code flags ...

Page 93

MULXU (multiply extend as unsigned) Operation Assembly-Language Format MULXU Rs, Rd Operand Size Byte Description This instruction performs 8-bit a source register and places the result in the destination register. The source register is an 8-bit ...

Page 94

Section 2 Instruction Set 2.2.34 NEG (negate) Operation 0 – Assembly-Language Format NEG Rd Operand Size Byte Description This instruction replaces the contents of an 8-bit general register with its two's complement (subtracts the register contents from H'00). ...

Page 95

NOP (no operation) Operation Assembly-Language Format NOP Operand Size — Description This instruction only increments the program counter, causing the next instruction to be executed. The internal state of the CPU does not change. Instruction ...

Page 96

Section 2 Instruction Set 2.2.36 NOT (NOT = logical complement) Operation ¬ Assembly-Language Format NOT Rd Operand Size Byte Description This instruction replaces the contents of an 8-bit general register with its one’s complement (subtracts the register contents ...

Page 97

OR (inclusive OR logical) Operation Rd (EAs) Rd Assembly-Language Format OR <EAs>, Rd Operand Size Byte Description This instruction ORs the source operand with the contents of an 8-bit general register and places the result in the general register. ...

Page 98

Section 2 Instruction Set 2.2.38 ORC (inclusive OR control register) Operation CCR #IMM CCR Assembly-Language Format ORC #xx:8, CCR Operand Size Byte Description This instruction ORs the condition code register (CCR) with immediate data and places the result in the ...

Page 99

POP (pop data) Operation @SP+ Rn Assembly-Language Format POP Rn Operand Size Word Description This instruction pops data from the stack to a 16-bit general register and sets condition code flags according to the data value. POP ...

Page 100

Section 2 Instruction Set 2.2.40 PUSH (push data) Operation Rn @–SP Assembly-Language Format PUSH Rn Operand Size Word Description This instruction pushes data from a 16-bit general register onto the stack and sets condition code flags according to the data ...

Page 101

ROTL (rotate left) Operation Rd (rotated left) Rd Assembly-Language Format ROTL Rd Operand Size Byte Description This instruction rotates an 8-bit general register one bit to the left. The most significant bit is rotated to the least significant bit, ...

Page 102

Section 2 Instruction Set 2.2.42 ROTR (rotate right) Operation Rd (rotated right) Rd Assembly-Language Format ROTR Rd Operand Size Byte Description This instruction rotates an 8-bit general register one bit to the right. The least significant bit is rotated to ...

Page 103

ROTXL (rotate with extend carry left) Operation Rd (rotated with carry left) Rd Assembly-Language Format ROTXL Rd Operand Size Byte Description This instruction rotates an 8-bit general register one bit to the left through the carry flag. The carry ...

Page 104

Section 2 Instruction Set 2.2.44 ROTXR (rotate with extend carry right) Operation Rd (rotated with carry right) Assembly-Language Format ROTXR Rd Operand Size Byte Description This instruction rotates an 8-bit general register one bit to the right through the carry ...

Page 105

RTE (return from exception) Operation @SP+ CCR @SP+ PC Assembly-Language Format RTE Operand Size — Description This instruction returns from an exception-handling routine. It pops the condition code register (CCR) and program counter (PC) from the stack. Program execution ...

Page 106

Section 2 Instruction Set 2.2.46 RTS (return from subroutine) Operation @SP+ PC Assembly-Language Format RTS Operand Size — Description This instruction returns from a subroutine. It pops the program counter (PC) from the stack. Program execution continues from the address ...

Page 107

SHAL (shift arithmetic left) Operation Rd (shifted arithmetic left ) Rd Assembly-Language Format SHAL Rd Operand Size Byte Description This instruction shifts an 8-bit general register one bit to the left. The most significant bit shifts into the carry ...

Page 108

Section 2 Instruction Set 2.2.48 SHAR (shift arithmetic right) Operation Rd (shifted arithmetic right ) Assembly-Language Format SHAR Rd Operand Size Byte Description This instruction shifts an 8-bit general register one bit to the right. The most significant bit remains ...

Page 109

SHLL (shift logical left) Operation Rd (shifted logical left ) Rd Assembly-Language Format SHLL Rd Operand Size Byte Description This instruction shifts an 8-bit general register one bit to the left. The least significant bit is cleared to 0. ...

Page 110

Section 2 Instruction Set 2.2.50 SHLR (shift logical right) Operation Rd (shifted logical right ) Rd Assembly-Language Format SHLR Rd Operand Size Byte Description This instruction shifts an 8-bit general register one bit to the right. The most significant bit ...

Page 111

SLEEP (sleep) Operation Program execution state power-down mode Assembly-Language Format SLEEP Operand Size — Description When the SLEEP instruction is executed, the CPU enters a power-down mode. Its internal state remains unchanged, but the CPU stops executing instructions and ...

Page 112

Section 2 Instruction Set 2.2.52 STC (store from control register) Operation CCR Rd Assembly-Language Format STC CCR, Rd Operand Size Byte Description This instruction copies the condition code register (CCR specified general register. Bits 6 and 4 are ...

Page 113

SUB (subtract binary) (byte) Operation Rd – Assembly-Language Format SUB.B Rs, Rd Operand Size Byte Description This instruction subtracts an 8-bit source register from an 8-bit destination register and places the result in the destination register. ...

Page 114

Section 2 Instruction Set 2.2.53 (2) SUB (subtract binary) (word) Operation Assembly-Language Format SUB.W Rs, Rd Operand Size Word Description This instruction subtracts a 16-bit source register from a 16-bit destination register and places the result ...

Page 115

SUBS (subtract with sign extension) Operation Rd – – Assembly-Language Format SUBS #1, Rd SUBS #2, Rd Operand Size Word Description This instruction subtracts the immediate value from word data in ...

Page 116

Section 2 Instruction Set 2.2.55 SUBX (subtract with extend carry) Operation Rd – (EAs) – Assembly-Language Format SUBX <EAs>, Rd Operand Size Byte Description This instruction subtracts the source operand and carry flag from the contents of an ...

Page 117

XOR (exclusive OR logical) Operation Rd (EAs) Rd Assembly-Language Format XOR <EAs>, Rd Operand Size Byte Description This instruction exclusive-ORs the source operand with the contents of an 8-bit general register and places the result in the general register. ...

Page 118

Section 2 Instruction Set 2.2.57 XORC (exclusive OR control register) Operation CCR #IMM CCR Assembly-Language Format XORC #xx:8, CCR Operand Size Byte Description This instruction exclusive-ORs the condition code register (CCR) with immediate data and places the result in the ...

Page 119

Operation Code Map Table 2-1 shows the operation code map for instructions of the H8/300L CPU. Only the first byte (bits the first word) of the instruction code is indicated here. Indicates that the most ...

Page 120

Section 2 Instruction Set Rev. 2.00 Dec 27, 2004 page 106 of 128 REJ09B0214-0200 ...

Page 121

List of Instructions Table 2-2 List of Instructions (1) Mnemonic Operation MOV.B #xx: #xx:8 MOV.B Rs Rs8 MOV.B @Rs @Rs16 MOV.B @(d:16, Rs @(d:16, Rs16) MOV.B @Rs @Rs16 Rs16+1 ...

Page 122

Section 2 Instruction Set Table 2-2 List of Instructions (2) Operation Mnemonic ADD.B #xx: Rd8+#xx:8 ADD.B Rs Rd8+Rs8 ADD.W Rs Rd16+Rs16 ADDX.B #xx: Rd8+#xx:8+C ADDX.B Rs Rd8+Rs8+C ADDS.W #1, Rd ...

Page 123

Table 2-2 List of Instructions (3) Operation Mnemonic SHAL SHAR SHLL SHLR ROTXL ROTXR ROTL ROTR BSET #xx:3, Rd ...

Page 124

Section 2 Instruction Set Table 2-2 List of Instructions (4) Mnemonic Operation BCLR #xx: (#xx:3 of Rd8) BCLR #xx:3, @Rd B (#xx:3 of @Rd16) BCLR #xx:3, @aa:8 B (#xx:3 of @aa:8) BCLR Rn (Rn8 of Rd8) ...

Page 125

Table 2-2 List of Instructions (5) Mnemonic Operation BIST #xx: BIST #xx:3, @ BIST #xx:3, @aa BAND #xx: (#xx:3 of Rd8) BAND #xx:3, @ (#xx:3 of @Rd16) BAND ...

Page 126

Section 2 Instruction Set Table 2-2 List of Instructions (6) Mnemonic Operation if condition BPL d:8 — is true then BMI d:8 — PC BGE d:8 — PC+d:8 else next; BLT d:8 — BGT d:8 — BLE d:8 — JMP ...

Page 127

Table 2-2 List of Instructions (7) Mnemonic Operation XORC #xx:8, CCR B CCR #xx:8 NOP — PC EEPMOV — if R4L Repeat @R5 Until R4L = 0 else next; Notes: * The number of execution states indicated here assumes that ...

Page 128

Section 2 Instruction Set 2.5 Number of Execution States The tables here can be used to calculate the number of states required for instruction execution. Table 2-3 indicates the number of states required for each cycle (instruction fetch, branch address ...

Page 129

Table 2-3 Number of States Taken by Each Cycle in Instruction Execution Execution Status (instruction cycle) Instruction fetch S I Branch address read S J Stack operation K S Byte data access S L Word data access S M Internal ...

Page 130

Section 2 Instruction Set Table 2-4 Number of Cycles in Each Instruction Instruction Mnemonic ADD ADD.B #xx:8, Rd ADD.B Rs, Rd ADD.W Rs, Rd ADDS ADDS.W #1/2, Rd ADDX ADDX.B #xx:8, Rd ADDX.B Rs, Rd AND AND.B #xx:8, Rd AND.B ...

Page 131

Instruction Mnemonic BCLR BCLR #xx:3, Rd BCLR #xx:3, @Rd BCLR #xx:3, @aa:8 BCLR Rn, Rd BCLR Rn, @Rd BCLR Rn, @aa:8 BIAND BIAND #xx:3, Rd BIAND #xx:3, @Rd BIAND #xx:3, @aa:8 BILD BILD #xx:3, Rd BILD #xx:3, @Rd BILD #xx:3, ...

Page 132

Section 2 Instruction Set Instruction Mnemonic BOR BOR #xx:3, Rd BOR #xx:3, @Rd BOR #xx:3, @aa:8 BSET BSET #xx:3, Rd BSET #xx:3, @Rd BSET #xx:3, @aa:8 BSET Rn, Rd BSET Rn, @Rd BSET Rn, @aa:8 BSR BSR d:8 BST BST ...

Page 133

Instruction Mnemonic JMP JMP @Rn JMP @aa:16 JMP @@aa:8 JSR JSR @Rn JSR @aa:16 JSR @@aa:8 LDC LDC #xx:8, CCR LDC Rs, CCR MOV MOV.B #xx:8, Rd MOV.B Rs, Rd MOV.B @Rs, Rd MOV.B @(d:16, Rs), Rd MOV.B @Rs+, Rd ...

Page 134

Section 2 Instruction Set Instruction Mnemonic NEG NEG.B Rd NOP NOP NOT NOT OR.B #xx:8, Rd OR.B Rs, Rd ORC ORC #xx:8, CCR POP POP Rd PUSH PUSH Rs ROTL ROTL.B Rd ROTR ROTR.B Rd ROTXL ROTXL.B Rd ...

Page 135

Section 3 CPU Operation States There are three CPU operation states, namely, program execution state, power-down state, and exception-handling state. In power-down state there are sleep mode, standby mode, and watch mode. These operation states are shown in figure 3-1. ...

Page 136

Section 3 CPU Operation States Reset state Reset occurs Power-down state Note: On the transitions between modes, see the applicable hardware manual. 3.1 Program Execution State In program execution state the CPU executes program instructions in sequence. 3.2 Exception Handling ...

Page 137

Table 3-1 Types of Exception Handling and Priorities Priority Exception source High Reset Interrupt Low Note: * Interrupt detection is not made upon completion of ANDC, ORC, XORC, and LDC instruction execution, nor upon completion of reset exception handling. 3.2.2 ...

Page 138

Section 3 CPU Operation States 3.2.3 Outline of Exception Handling Operation A reset has the highest priority of all exception handling. After the RES pin goes to low level putting the CPU in reset state, the RES pin is then ...

Page 139

Reset State When the RES pin goes to low level, all processing stops and the system goes to reset state. The I bit of the condition code register (CCR) is set, masking all interrupts. After the RES pin is ...

Page 140

Section 3 CPU Operation States Rev. 2.00 Dec 27, 2004 page 126 of 128 REJ09B0214-0200 ...

Page 141

Section 4 Basic Operation Timing CPU operation is synchronized by a clock f). The period from the rising edge of to the next rising edge is called one state. A memory cycle or bus cycle consists of two or three ...

Page 142

Section 4 Basic Operation Timing 4.2 On-chip Peripheral Modules and External Devices On-chip peripheral modules are accessed in two or three states. The data bus width is 8 bits, so access is made in byte size only. Access to word ...

Page 143

Renesas 16-Bit Single-Chip Microcomputer Software Manual H8/300L Series Publication Date: 1st Edition, December 1991 Rev.2.00, December 27, 2004 Published by: Sales Strategic Planning Div. Renesas Technology Corp. Edited by: Technical Documentation & Information Department Renesas Kodaira Semiconductor Co., Ltd. © ...

Page 144

RENESAS SALES OFFICES Refer to "http://www.renesas.com/en/network" for the latest and detailed information. Renesas Technology America, Inc. 450 Holger Way, San Jose, CA 95134-1368, U.S.A Tel: <1> (408) 382-7500, Fax: <1> (408) 382-7501 Renesas Technology Europe Limited Dukes Meadow, Millboard Road, ...

Page 145

Shimonumabe, Nakahara-ku, Kawasaki-shi, Kanagawa 211-8668 Japan H8/300L Series Software Manual REJ09B0214-0200 ...