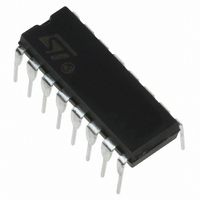

ST62T00CB6 STMicroelectronics, ST62T00CB6 Datasheet - Page 27

ST62T00CB6

Manufacturer Part Number

ST62T00CB6

Description

IC MCU 8BIT OTP 1K 16-PDIP

Manufacturer

STMicroelectronics

Series

ST6r

Specifications of ST62T00CB6

Core Processor

ST6

Core Size

8-Bit

Speed

8MHz

Peripherals

LVD, POR, WDT

Number Of I /o

9

Program Memory Size

1KB (1K x 8)

Program Memory Type

OTP

Ram Size

64 x 8

Voltage - Supply (vcc/vdd)

3 V ~ 6 V

Data Converters

A/D 4x8b

Oscillator Type

Internal

Operating Temperature

-40°C ~ 85°C

Package / Case

16-DIP (0.300", 7.62mm)

Controller Family/series

ST6

No. Of I/o's

9

Ram Memory Size

64Byte

Cpu Speed

8MHz

No. Of Timers

1

Rohs Compliant

Yes

Processor Series

ST62T0x

Core

ST6

Data Bus Width

8 bit

Data Ram Size

64 B

Maximum Clock Frequency

8 MHz

Number Of Programmable I/os

9

Number Of Timers

2

Operating Supply Voltage

3 V to 6 V

Maximum Operating Temperature

+ 85 C

Mounting Style

Through Hole

Development Tools By Supplier

ST622XC-KIT/110, ST62GP-EMU2, ST62E2XC-EPB/110, ST62E6XC-EPB/US, STREALIZER-II

Minimum Operating Temperature

- 40 C

On-chip Adc

8 bit

Cpu Family

ST6

Device Core Size

8b

Frequency (max)

8MHz

Total Internal Ram Size

64Byte

# I/os (max)

9

Number Of Timers - General Purpose

1

Operating Supply Voltage (typ)

3.3/5V

Operating Supply Voltage (max)

6V

Operating Supply Voltage (min)

3V

Instruction Set Architecture

CISC

Operating Temp Range

-40C to 85C

Operating Temperature Classification

Industrial

Mounting

Through Hole

Pin Count

16

Package Type

PDIP

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Eeprom Size

-

Connectivity

-

Lead Free Status / Rohs Status

In Transition

Other names

497-2093-5

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

ST62T00CB6

Manufacturer:

MICRON

Quantity:

1 450

Company:

Part Number:

ST62T00CB6

Manufacturer:

STMicroelectronics

Quantity:

135

INTERRUPTS (Cont’d)

3.4.2 Interrupt Procedure

The interrupt procedure is very similar to a call pro-

cedure, indeed the user can consider the interrupt

as an asynchronous call procedure. As this is an

asynchronous event, the user cannot know the

context and the time at which it occurred. As a re-

sult, the user should save all Data space registers

which may be used within the interrupt routines.

There are separate sets of processor flags for nor-

mal, interrupt and non-maskable interrupt modes,

which are automatically switched and so do not

need to be saved.

The following list summarizes the interrupt proce-

dure:

MCU

– The interrupt is detected.

– The C and Z flags are replaced by the interrupt

– The PC contents are stored in the first level of

– The normal interrupt lines are inhibited (NMI still

– The first internal latch is cleared.

– Theassociated interrupt vectoris loaded inthe PC.

WARNING: In some circumstances, when a

maskable interrupt occurs while the ST6 core is in

NORMAL mode and especially during the execu-

tion of an ”ldi IOR, 00h” instruction (disabling all

maskable interrupts): if the interrupt arrives during

the first 3 cycles of the ”ldi” instruction (which is a

4-cycle instruction) the core will switch to interrupt

mode BUT the flags CN and ZN will NOT switch to

the interrupt pair CI and ZI.

User

– User selected registers are saved within the in-

– The source of the interrupt is found by polling the

– The interrupt is serviced.

– Return from interrupt (RETI)

flags (or by the NMI flags).

the stack.

active).

terrupt service routine (normally on a software

stack).

interrupt flags (if more than one source is associ-

ated with the same vector).

MCU

– Automatically the MCU switches back to the nor-

The interrupt routine usually begins by the identify-

ing the device which generated the interrupt re-

quest (by polling). The user should save the regis-

ters which are used within the interrupt routine in a

software stack. After the RETI instruction is exe-

cuted, the MCU returns to the main routine.

Figure 20. Interrupt Processing Flow Chart

mal flag set (or the interrupt flag set) and pops

the previous PC value from the stack.

YES

NO

PROGRAM FLAGS

THE INS TRU CTION

INT ERR UP T MASK

THE STACK ED PC

IN STRUC TION

INS TRU CTION

INS TRU CTION

EXEC UTE

A RE TI

ST62T00C/T01C ST62T03C/E01C

SELECT

WAS

FETCH

C LEAR

”POP”

?

?

YES

N O

YES

?

NORMAL MODE?

AN IN TER RUP T R EQUEST

NO

AN D INTE RRU PT MASK

IS THE CORE

ALREADY IN

C HEC K IF THER E IS

IN TERNA L MODE FLAG

PC IN TO THE STACK

INT ERR UP T VEC TOR

INTER RU PT MASK

LOAD PC FROM

PUSH THE

(FFC/FFD)

SELECT

SET

VA000014

27/70

27