73S1209F-44IM/F Maxim Integrated Products, 73S1209F-44IM/F Datasheet - Page 86

73S1209F-44IM/F

Manufacturer Part Number

73S1209F-44IM/F

Description

IC SMART CARD READER 44-QFN

Manufacturer

Maxim Integrated Products

Datasheet

1.73S1209F-44IMF.pdf

(93 pages)

Specifications of 73S1209F-44IM/F

Core Processor

80515

Core Size

8-Bit

Speed

24MHz

Connectivity

I²C, SmartCard, UART/USART

Peripherals

LED, POR, WDT

Number Of I /o

9

Program Memory Size

32KB (32K x 8)

Program Memory Type

FLASH

Ram Size

2K x 8

Voltage - Supply (vcc/vdd)

2.7 V ~ 5.5 V

Oscillator Type

Internal

Operating Temperature

-40°C ~ 85°C

Package / Case

*

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Eeprom Size

-

Data Converters

-

Lead Free Status / Rohs Status

Lead free / RoHS Compliant

73S12xxF Software User Guide

UG_12xxF_016

4.5.1 EMV LEVEL I Certification Tests

The EMV compliant test suite follows the Payment System Environment specification. There are several

test labs, listed on the

www.emvco.com

website, qualified to perform these tests.

Currently, there are two available Protocol test suites that can be used to qualify for EMV Level I

compliance. Passing either of these suites will qualify as EMV Level I compliance. The Pseudo-CCID

code links to the two TSC libraries LAPI and HAPI which comply with both tests. However, since each

lab has its own test scripts and the test scripts differ according to the lab’s setup, the application layer

must be written and adapted specifically for each test lab’s requirements. The following subsections

describe the loopback tests that are to be written either on the host side or added to the TSC Pseudo-

CCID firmware.

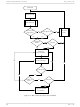

4.5.1.1 EMV Test Mode

An EMV test (or session) is defined as a Command/Response pair that runs from the Activation of the

card to the Deactivation of the card. A Block Transfer may or may not occur during the session

depending on the card’s ATR response.

The host may set up the EMV PSE test environment via the USB CCID Card Control command (Escape

command). The first parameter byte (B1) of the Escape command must specifically indicate whether a

test mode is invoked and if so, it should be invoked using the MCI, VISA I or VISA II test environment.

Review the Escape command section for details about this test mode.

Following a successful Escape command, the host should start the test by sending the PowerOn

command (ScardConnect). Depending on the status of the ATR (good or bad), the host should send an

empty Block Transfer command without the APDU command (command length = 0). For example: 6F

00 00 00 00… CRC.

The test loopback will be handled by the firmware and upon completion of each test, the firmware will

respond to the host with the status, indicating whether the test session completed with a successful

return code or not. An unsuccessful return code may or may not indicate that the test failed. The test

result (test passed or test failed) is determined only by the card side.

Figure 11

depicts the minimal coding required on the host side to invoke the EMV PSE test environment.

86

Rev. 1.50