MSC7118VM1200 Freescale Semiconductor, MSC7118VM1200 Datasheet - Page 35

MSC7118VM1200

Manufacturer Part Number

MSC7118VM1200

Description

DSP 16BIT W/DDR CTRLR 400-MAPBGA

Manufacturer

Freescale Semiconductor

Series

MSC711x StarCorer

Type

Fixed Pointr

Datasheet

1.KMSC7118VF1200.pdf

(60 pages)

Specifications of MSC7118VM1200

Interface

Host Interface, I²C, UART

Clock Rate

300MHz

Non-volatile Memory

ROM (8 kB)

On-chip Ram

464kB

Voltage - I/o

3.30V

Voltage - Core

1.20V

Operating Temperature

-40°C ~ 105°C

Mounting Type

*

Package / Case

400-MAPBGA

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

MSC7118VM1200

Manufacturer:

Freescale Semiconductor

Quantity:

10 000

2.5.8

2.5.9

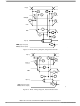

Figure 20 shows the signal behavior of the

Freescale Semiconductor

Notes:

No.

400

401

402

—

—

Number

65

66

Internal bus clock (APBCLK)

Internal bus clock period (1/APBCLK)

URXD and UTXD inputs high/low duration

URXD and UTXD inputs rise/fall time

UTXD output rise/fall time

1.

2.

3.

UART Timing

EE Timing

The core clock is the SC1400 core clock. The ratio between the core clock and CLKOUT is configured during power-on-reset.

Configure the direction of the EE pin in the EE_CTRL register (see the SC140/SC1400 Core Reference Manual for details.

Refer to Table 1-11 on page 1-16 for details on EE pin functionality.

UTXD, URXD

UTXD Output

EE0 input to the core

EE0 output from the core

inputs

MSC7118 Low-Cost 16-bit DSP with DDR Controller Data Sheet, Rev. 7

Characteristics

Characteristics

EE0 Out

EE0 In

EE

Figure 18. UART Output Timing

Figure 17. UART Input Timing

pin.

401

402

Figure 19. EE Pin Timing

Table 23. UART Timing

Table 24. EE0 Timing

400

Synchronous to core clock

Asynchronous

Type

Expression

16 × T

F

T

CORE

APBCLK

APBCLK

402

/2

66

65

401

400

106.67

Min

6.67

—

—

—

4 core clock periods

1 core clock period

Max

150

—

—

5

5

Min

Unit

MHz

ns

ns

ns

ns

35