CY7C1019DV33-10BVXIT Cypress Semiconductor Corp, CY7C1019DV33-10BVXIT Datasheet

CY7C1019DV33-10BVXIT

Specifications of CY7C1019DV33-10BVXIT

Available stocks

Related parts for CY7C1019DV33-10BVXIT

CY7C1019DV33-10BVXIT Summary of contents

Page 1

... The eight input/output pins (I/O high-impedance state when the device is deselected (CE HIGH), the outputs are disabled (OE HIGH), or during a write operation (CE LOW, and WE LOW). The CY7C1019DV33 is available in Pb-free 32-pin 400-Mil wide Molded SOJ, 32-pin TSOP II and 48-ball VFBGA packages. INPUTBUFFER 128K × 8 ...

Page 2

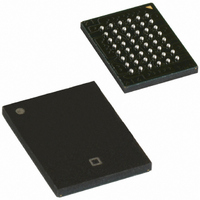

... Maximum Operating Current Maximum Standby Current [2] Pin Configurations 48-ball VFBGA (Top View Note 2. NC pins are not connected on the die. Document #: 38-05481 Rev. *E –10 (Industrial I I I/O I CY7C1019DV33 Unit SOJ/TSOPII Top View I I/O I I I Page [+] Feedback ...

Page 3

... MAX RC 66MHz 40MHz Max > > < MAX Max > V – 0.3V > V – 0. < 0.3V CY7C1019DV33 [3] ................................ –0. 0.3V CC Ambient V Speed CC Temperature 3.3V 0.3V –40C to +85 –10 (Industrial) Unit Min. Max. 2.4 V 0 –0.3 0.8 V A –1 +1 A – ...

Page 4

... A CC Test Conditions Still Air, soldered × 4.5 inch, four-layer printed circuit board [5] 3.0V GND 30 pF* Rise Time: 1 V/ns High-Z characteristics: R1 317 3.3V OUTPUT 351 (c) CY7C1019DV33 Max. Unit SOJ TSOP II VFBGA Unit C/W 56.29 62.22 36 C/W 38.14 21.43 9 ALL INPUT PULSES ...

Page 5

... The minimum write cycle time for Write Cycle no. 3 (WE controlled, OE LOW) is the sum of t Document #: 38-05481 Rev. *E [6] Min. 100 values until the first memory access can be performed CC is less than less than t , and t HZCE LZCE HZOE LZOE HZWE and t HZWE CY7C1019DV33 –10 (Industrial) Unit Max. ...

Page 6

... CE > > V – 0. < 0. DATA RETENTION MODE 3.0V > CDR [14, 15 OHA DOE DATA VALID 50% > 50 s or stable at V > 50 CC(min.) CC(min.) CY7C1019DV33 Min. Max. Unit 2.0 V – 0.3V 3. DATA VALID t HZOE t HZCE HIGH IMPEDANCE t PD ICC 50% ISB Page [+] Feedback ...

Page 7

... If CE goes HIGH simultaneously with WE going HIGH, the output remains in a high-impedance state. 19. During this period the I/Os are in the output state and input signals should not be applied. Document #: 38-05481 Rev SCE SA t SCE PWE t SD DATA VALID [17, 18 SCE PWE t SD DATA VALID IN CY7C1019DV33 Page [+] Feedback ...

Page 8

... Write Cycle No. 3 (WE Controlled, OE LOW) ADDRESS DATA I/O NOTE 19 t HZWE Truth Table I/O –I High Data Out Data High Z Document #: 38-05481 Rev. *E [12, 18 SCE PWE t SD DATA VALID Mode 7 Power-Down Read Write Selected, Outputs Disabled CY7C1019DV33 LZWE Power Standby ( Active ( Active ( Active ( Page [+] Feedback ...

Page 9

... Package Type: XXX = VX or ZSX or BVX VX = 32-pin Molded SOJ (Pb-free) ZSX = 32-pin TSOP Type II (Pb-free) BVX = 48-ball VFBGA (Pb-free) Speed V33 = Voltage range ( 3 C9 Technology 9 = Data width × 8-bits 01 = 1-Mbit density 1 = Fast Asynchronous SRAM family Technology Code CMOS 7 = SRAM CY = Cypress CY7C1019DV33 Operating Range Industrial Page [+] Feedback ...

Page 10

... Package Diagrams Figure 1. 32-pin (400-Mil) Molded SOJ (51-85033) Figure 2. 32-pin Thin Small Outline Package Type II (51-85095) Document #: 38-05481 Rev. *E CY7C1019DV33 51-85033 *C 51-85095 *A Page [+] Feedback ...

Page 11

... Package Diagrams (continued) Figure 3. 48-ball VFBGA ( mm) (51-85150) All product and company names mentioned in this document are the trademarks of their respective holders. Document #: 38-05481 Rev. *E CY7C1019DV33 51-85150 *F Page [+] Feedback ...

Page 12

... Document History Page Document Title: CY7C1019DV33, 1-Mbit (128K x 8) Static RAM Document Number: 38-05481 REV. ECN NO. Issue Date ** 201560 See ECN *A 233750 See ECN *B 262950 See ECN *C 307598 See ECN *D 520652 See ECN *E 3110052 12/14/2010 Document #: 38-05481 Rev. *E Orig. of Description of Change ...

Page 13

... The inclusion of Cypress products in life-support systems application implies that the manufacturer assumes all risk of such use and in doing so indemnifies Cypress against all charges. cypress.com/go/plc CY7C1019DV33 PSoC Solutions psoc.cypress.com/solutions ...