BLD6G21L-50,112 NXP Semiconductors, BLD6G21L-50,112 Datasheet

BLD6G21L-50,112

Specifications of BLD6G21L-50,112

Available stocks

Related parts for BLD6G21L-50,112

BLD6G21L-50,112 Summary of contents

Page 1

... Rev. 2 — 17 August 2010 1. Product profile 1.1 General description The BLD6G21L-50 and BLD6G21LS-50 incorporate a fully integrated Doherty solution using NXP’s state of the art GEN6 LDMOS technology. This device is perfectly suited for TD-SCDMA base station applications at frequencies from 2010 MHz to 2025 MHz. The main and peak device, input splitter and output combiner are integrated in a single package ...

Page 2

... BLD6G21LS-50 (SOT1130B [1] Connected to flange. 3. Ordering information Table 3. Type number BLD6G21L-50 BLD6G21LS-50 - BLD6G21L-50_BLD6G21LS-50 Product data sheet BLD6G21L-50; BLD6G21LS-50 TD-SCDMA 2010 MHz to 2025 MHz fully integrated Doherty transistor Pinning Description drain gate + bias main source n.c. bias peak drain gate + bias main source n ...

Page 3

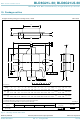

... Product data sheet BLD6G21L-50; BLD6G21LS-50 TD-SCDMA 2010 MHz to 2025 MHz fully integrated Doherty transistor 2 RF-input/bias main 90 5 bias peak Block diagram of BLD6G21L-50 and BLD6G21LS-50 Limiting values Parameter drain-source voltage main amplifier gate-source voltage peak amplifier gate-source voltage drain current storage temperature ...

Page 4

... Mode of operation: Pulsed CW; V GS(amp)peak Symbol P L(3dB) 8.1 Ruggedness in Doherty operation The BLD6G21L-50 and BLD6G21LS-50 are capable of withstanding a load mismatch corresponding to VSWR = through all phases under the following conditions 8.2 Impedance information Table 9. Measured Load Pull data; typical values unless otherwise specified. ...

Page 5

... NXP Semiconductors Fig 2. 8.3 Performance curves Performance curves are measured in a BLD6G21L-50 application circuit. 8.3.1 CW pulsed (dB) 15 (6) (5) (4) 13 (3) (2) ( 170 mA (main 2017.5 MHz; δ ( GS(amp)peak ( 0.2 V GS(amp)peak ( 0.4 V GS(amp)peak ( 0.5 V GS(amp)peak ( 0.6 V GS(amp)peak ( 0.8 V GS(amp)peak Fig 3. Power gain as a function of load power; ...

Page 6

... MHz ( 2018 MHz ( 2025 MHz Fig 5. Power gain as a function of load power; typical values ( 2010 MHz ( 2018 MHz ( 2025 MHz Fig 7. BLD6G21L-50_BLD6G21LS-50 Product data sheet BLD6G21L-50; BLD6G21LS-50 TD-SCDMA 2010 MHz to 2025 MHz fully integrated Doherty transistor 001aam430 (%) (1) (2) ( (dBm °C; ...

Page 7

... V GS(amp)peak ( 0.5 V GS(amp)peak ( 0.6 V GS(amp)peak ( 0.8 V GS(amp)peak Fig 8. Power gain as a function of average load power; typical values BLD6G21L-50_BLD6G21LS-50 Product data sheet BLD6G21L-50; BLD6G21LS-50 TD-SCDMA 2010 MHz to 2025 MHz fully integrated Doherty transistor 001aam433 (6) (5) (4) (3) (2) ( (dBm) L(AV °C; case Fig 9. ...

Page 8

... V; 6-carrier TD-SCDMA; PAR = 10.8 dB GS(amp)peak at 0.01 % probability on CCDF. ( 2010 MHz ( 2018 MHz ( 2025 MHz Fig 11. Power gain as a function of average load power; typical values BLD6G21L-50_BLD6G21LS-50 Product data sheet BLD6G21L-50; BLD6G21LS-50 TD-SCDMA 2010 MHz to 2025 MHz fully integrated Doherty transistor (dB) 15 14.5 ...

Page 9

... C7, C8 C9, C10 C11, C13, C14, C16 C17 C19, C20 C21 L1 [1] American Technical Ceramics type 100B or capacitor of same quality. BLD6G21L-50_BLD6G21LS-50 Product data sheet BLD6G21L-50; BLD6G21LS-50 TD-SCDMA 2010 MHz to 2025 MHz fully integrated Doherty transistor V GS(amp)main INPUT C19 C21 C20 C4 R2 The striplines are on a double copper-clad gold plated Rogers 4350B Printed-Circuit Board (PCB) with ε ...

Page 10

... Note 1. millimeter dimensions are derived from the original inch dimensions. 2. dimension is measured 0.030 inch (0.76 mm) from the body. Outline version IEC SOT1130A Fig 14. Package outline SOT1130A BLD6G21L-50_BLD6G21LS-50 Product data sheet BLD6G21L-50; BLD6G21LS-50 TD-SCDMA 2010 MHz to 2025 MHz fully integrated Doherty transistor ...

Page 11

... Note 1. millimeter dimensions are derived from the original inch dimensions. 2. dimension is measured 0.030 inch (0.76 mm) from the body. Outline version IEC SOT1130B Fig 15. Package outline SOT1130B BLD6G21L-50_BLD6G21LS-50 Product data sheet BLD6G21L-50; BLD6G21LS-50 TD-SCDMA 2010 MHz to 2025 MHz fully integrated Doherty transistor ...

Page 12

... Table 12. Revision history Document ID BLD6G21L-50_BLD6G21LS-50 v.2 Modifications: BLD6G21L-50_BLD6G21LS-50 v.1 BLD6G21L-50_BLD6G21LS-50 Product data sheet BLD6G21L-50; BLD6G21LS-50 TD-SCDMA 2010 MHz to 2025 MHz fully integrated Doherty transistor Abbreviations Description Complementary Cumulative Distribution Function Continuous Wave Laterally Diffused Metal-Oxide Semiconductor Peak-to-Average power Ratio Radio Frequency ...

Page 13

... BLD6G21L-50_BLD6G21LS-50 Product data sheet BLD6G21L-50; BLD6G21LS-50 TD-SCDMA 2010 MHz to 2025 MHz fully integrated Doherty transistor [3] Definition This document contains data from the objective specification for product development. ...

Page 14

... For sales office addresses, please send an email to: BLD6G21L-50_BLD6G21LS-50 Product data sheet BLD6G21L-50; BLD6G21LS-50 TD-SCDMA 2010 MHz to 2025 MHz fully integrated Doherty transistor NXP Semiconductors’ specifications such use shall be solely at customer’s own risk, and (c) customer fully indemnifies NXP Semiconductors for any liability, damages or failed product claims resulting from customer design and use of the product for automotive applications beyond NXP Semiconductors’ ...

Page 15

... Please be aware that important notices concerning this document and the product(s) described herein, have been included in section ‘Legal information’. © NXP B.V. 2010. For more information, please visit: http://www.nxp.com For sales office addresses, please send an email to: salesaddresses@nxp.com All rights reserved. Date of release: 17 August 2010 Document identifier: BLD6G21L-50_BLD6G21LS-50 ...