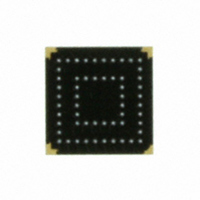

XC2C32A-6CPG56C Xilinx Inc, XC2C32A-6CPG56C Datasheet - Page 2

XC2C32A-6CPG56C

Manufacturer Part Number

XC2C32A-6CPG56C

Description

CPLD CoolRunner™-II Family 750 Gates 32 Macro Cells 200MHz 0.18um (CMOS) Technology 1.8V 56-Pin CSBGA

Manufacturer

Xilinx Inc

Series

CoolRunner IIr

Specifications of XC2C32A-6CPG56C

Package

56CSBGA

Family Name

CoolRunnerÂ-II

Device System Gates

750

Number Of Macro Cells

32

Maximum Propagation Delay Time

6 ns

Number Of User I/os

33

Number Of Logic Blocks/elements

2

Typical Operating Supply Voltage

1.8 V

Maximum Operating Frequency

200 MHz

Number Of Product Terms Per Macro

40

Operating Temperature

0 to 70 °C

Programmable Type

In System Programmable

Delay Time Tpd(1) Max

5.5ns

Voltage Supply - Internal

1.7 V ~ 1.9 V

Number Of Logic Elements/blocks

2

Number Of Macrocells

32

Number Of Gates

750

Number Of I /o

33

Mounting Type

Surface Mount

Package / Case

56-CSBGA

Features

Programmable

Voltage

1.8V

Memory Type

CMOS

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Number Of Logic Elements/cells

-

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Other names

122-1403

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

XC2C32A-6CPG56C

Manufacturer:

XilinxInc

Quantity:

3 000

Part Number:

XC2C32A-6CPG56C

Manufacturer:

XILINX/赛灵思

Quantity:

20 000

XC2C32A CoolRunner-II CPLD

RealDigital Design Technology

Xilinx® CoolRunner-II CPLDs are fabricated on a

0.18 micron process technology which is derived from lead-

ing edge FPGA product development. CoolRunner-II

CPLDs employ RealDigital, a design technique that makes

use of CMOS technology in both the fabrication and design

methodology. RealDigital design technology employs a cas-

cade of CMOS gates to implement sum of products instead

of traditional sense amplifier methodology. Due to this tech-

nology, Xilinx CoolRunner-II CPLDs achieve both high per-

formance and low power operation.

Supported I/O Standards

The CoolRunner-II CPLD 32 macrocell features both

LVCMOS and LVTTL I/O implementations. See

I/O standard voltages. The LVTTL I/O standard is a general

purpose EIA/JEDEC standard for 3.3V applications that use

an LVTTL input buffer and Push-Pull output buffer. The

Table 2: I

2

Notes:

1.

Typical I

16-bit up/down, resettable binary counter (one counter per function block).

CC

CC

(mA)

vs. Frequency (LVCMOS 1.8V T

0.016

15

10

20

0

5

0

0

0.87

25

50

Figure 1: I

A

Table 1

1.75

= 25°C)

50

100

www.xilinx.com

(1)

for

2.61

Frequency (MHz)

CC

75

vs. Frequency

150

LVCMOS standard is used in 3.3V, 2.5V, and 1.8V applica-

tions. CoolRunner-II CPLDs are also 1.5V I/O compatible

with the use of Schmitt-trigger inputs.

Table 1: I/O Standards for XC2C32A

1.

IOSTANDARD

LVTTL

LVCMOS33

LVCMOS25

LVCMOS18

LVCMOS15

3.44

100

Frequency (MHz)

Attribute

LVCMOS15 requires Schmitt-trigger inputs.

200

5.16

150

(1)

250

5.99

Output

175

V

DS091_01_030105

CCIO

3.3

3.3

2.5

1.8

1.5

300

6.81

200

V

Input

3.3

3.3

2.5

1.8

1.5

CCIO

DS310 (v2.1) November 6, 2008

7.63

225

Input

V

N/A

N/A

N/A

N/A

N/A

REF

Product Specification

8.36

250

Termination

Voltage V

Board

N/A

N/A

N/A

N/A

N/A

9.93

300

T

R