EPM9560ARI240-10 Altera, EPM9560ARI240-10 Datasheet - Page 5

EPM9560ARI240-10

Manufacturer Part Number

EPM9560ARI240-10

Description

IC MAX 9000 CPLD 560 240-RQFP

Manufacturer

Altera

Series

MAX® 9000r

Datasheet

1.EPM9320LC84-15.pdf

(46 pages)

Specifications of EPM9560ARI240-10

Programmable Type

In System Programmable

Delay Time Tpd(1) Max

10.0ns

Voltage Supply - Internal

4.5 V ~ 5.5 V

Number Of Logic Elements/blocks

35

Number Of Macrocells

560

Number Of Gates

12000

Number Of I /o

191

Operating Temperature

-40°C ~ 85°C

Mounting Type

Surface Mount

Package / Case

240-RQFP

Voltage

3.3V/5V

Memory Type

EEPROM

Number Of Logic Elements/cells

35

Family Name

MAX 9000

# Macrocells

560

Number Of Usable Gates

12000

Frequency (max)

144.9MHz

Propagation Delay Time

10ns

Number Of Logic Blocks/elements

35

# I/os (max)

191

Operating Supply Voltage (typ)

5V

In System Programmable

Yes

Operating Supply Voltage (min)

4.5V

Operating Supply Voltage (max)

5.5V

Operating Temp Range

-40C to 85C

Operating Temperature Classification

Industrial

Mounting

Surface Mount

Pin Count

240

Package Type

RQFP

Lead Free Status / RoHS Status

Contains lead / RoHS non-compliant

Features

-

Lead Free Status / Rohs Status

Not Compliant

Other names

544-2365

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

EPM9560ARI240-10

Manufacturer:

ALTERA

Quantity:

6

Part Number:

EPM9560ARI240-10

Manufacturer:

ALTERA/阿尔特拉

Quantity:

20 000

Altera Corporation

Functional

Description

f

The MAX 9000 family is supported by Altera’s MAX+PLUS II

development system, a single, integrated software package that offers

schematic, text—including VHDL, Verilog HDL, and the Altera

Hardware Description Language (AHDL)—and waveform design entry,

compilation and logic synthesis, simulation and timing analysis, and

device programming. The MAX+PLUS II software provides EDIF 2 0 0

and 3 0 0, LPM, and other interfaces for additional design entry and

simulation support from other industry-standard PC- and UNIX-

workstation-based EDA tools. The MAX+PLUS II software runs on

Windows-based PCs as well as Sun SPARCstation, HP 9000 Series

700/800, and IBM RISC System/6000 workstations.

For more information on development tools, see the

Programmable Logic Development System & Software Data

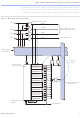

MAX 9000 devices use a third-generation MAX architecture that yields

both high performance and a high degree of utilization for most

applications. The MAX 9000 architecture includes the following elements:

Figure 1

Logic array blocks

Macrocells

Expander product terms (shareable and parallel)

FastTrack Interconnect

Dedicated inputs

I/O cells

shows a block diagram of the MAX 9000 architecture.

MAX 9000 Programmable Logic Device Family Data Sheet

MAX+PLUS II

Sheet.

5