EP2S60F484I4N Altera, EP2S60F484I4N Datasheet - Page 11

EP2S60F484I4N

Manufacturer Part Number

EP2S60F484I4N

Description

IC STRATIX II FPGA 60K 484-FBGA

Manufacturer

Altera

Series

Stratix® IIr

Datasheet

1.EP2S15F484I4N.pdf

(238 pages)

Specifications of EP2S60F484I4N

Number Of Logic Elements/cells

60440

Number Of Labs/clbs

3022

Total Ram Bits

2544192

Number Of I /o

334

Voltage - Supply

1.15 V ~ 1.25 V

Mounting Type

Surface Mount

Operating Temperature

-40°C ~ 100°C

Package / Case

484-FBGA

Family Name

Stratix II

Number Of Logic Blocks/elements

60440

# I/os (max)

334

Frequency (max)

711.24MHz

Process Technology

90nm (CMOS)

Operating Supply Voltage (typ)

1.2V

Logic Cells

60440

Ram Bits

2544192

Operating Supply Voltage (min)

1.15V

Operating Supply Voltage (max)

1.25V

Operating Temp Range

-40C to 100C

Operating Temperature Classification

Industrial

Mounting

Surface Mount

Pin Count

484

Package Type

FC-FBGA

For Use With

544-1700 - DSP KIT W/STRATIX II EP2S60N544-1697 - NIOS II KIT W/STRATIX II EP2S60N

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Number Of Gates

-

Lead Free Status / Rohs Status

Compliant

Other names

544-1910

EP2S60F484I4N

EP2S60F484I4N

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

EP2S60F484I4N

Manufacturer:

NANYA

Quantity:

30

Company:

Part Number:

EP2S60F484I4N

Manufacturer:

ALTERA

Quantity:

238

Part Number:

EP2S60F484I4N

Manufacturer:

ALTERA

Quantity:

20 000

Logic Array

Blocks

Altera Corporation

May 2007

EP2S15

EP2S30

EP2S60

EP2S90

EP2S130

EP2S180

Table 2–1. Stratix II Device Resources

Device

Columns/Blocks

M512 RAM

11 / 930

4 / 104

6 / 202

7 / 329

8 / 488

9 / 699

The number of M512 RAM, M4K RAM, and DSP blocks varies by device

along with row and column numbers and M-RAM blocks.

the resources available in Stratix II devices.

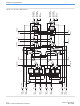

Each LAB consists of eight ALMs, carry chains, shared arithmetic chains,

LAB control signals, local interconnect, and register chain connection

lines. The local interconnect transfers signals between ALMs in the same

LAB. Register chain connections transfer the output of an ALM register to

the adjacent ALM register in an LAB. The Quartus

associated logic in an LAB or adjacent LABs, allowing the use of local,

shared arithmetic chain, and register chain connections for performance

and area efficiency.

Columns/Blocks

M4K RAM

4 / 144

5 / 255

6 / 408

7 / 609

8 / 768

3 / 78

Figure 2–2

M-RAM

Blocks

0

1

2

4

6

9

shows the Stratix II LAB structure.

Columns/Blocks

DSP Block

Stratix II Device Handbook, Volume 1

2 / 12

2 / 16

3 / 36

3 / 48

3 / 63

4 / 96

®

Columns

II Compiler places

Stratix II Architecture

LAB

100

30

49

62

71

81

Table 2–1

LAB Rows

26

36

51

68

87

96

lists

2–3