PX1011BI-EL1/G,551 NXP Semiconductors, PX1011BI-EL1/G,551 Datasheet

PX1011BI-EL1/G,551

Specifications of PX1011BI-EL1/G,551

PX1011BI-EL1/G-S

PX1011BI-EL1/G-S

Available stocks

Related parts for PX1011BI-EL1/G,551

PX1011BI-EL1/G,551 Summary of contents

Page 1

... The 8-bit data interface operates at 250 MHz with SSTL_2 signaling. The SSTL_2 signaling is compatible with the I/O interfaces available in FPGA products. The PX1011B PCI Express PHY supports advanced power management functions. The PX1011BI is for the industrial temperature range ( +85 C). 2. Features 2.1 PCI Express interface I Compliant to PCI Express Base Specifi ...

Page 2

... NXP Semiconductors 2.3 JTAG interface I JTAG (IEEE 1149.1) boundary scan interface I Built-In Self Test (BIST) controller tests SerDes and I/O blocks at speed I 3.3 V CMOS signaling 2.4 Power management I Dissipates < 300 normal mode I Support power management of L0, L0s and L1 2.5 Clock I 100 MHz external reference clock with 300 ppm tolerance ...

Page 3

... NXP Semiconductors 4. Ordering information Table 2. Ordering information Type number Solder process PX1011B-EL1/G Pb-free (SnAgCu solder ball compound) PX1011B-EL1/N SnPb solder ball compound PX1011BI-EL1/G Pb-free (SnAgCu solder ball compound) 5. Marking Table 3. Line Table 4. Line [1] Industrial temperature range. PX1011B_4 Product data sheet Package ...

Page 4

... NXP Semiconductors 6. Block diagram Fig 1. PX1011B_4 Product data sheet TXDATA [ 7:0 ] TXCLK RXCLK Ln_TxData0 Ln_TxData1 8b/10b ENCODE PARALLEL TO SERIAL 250 MHz clock CLK GENERATOR TX I/O REFCLK I/O TX_P TX_N REFCLK_P REFCLK_N Block diagram Rev. 04 — 4 September 2009 PX1011B PCI Express stand-alone X1 PHY ...

Page 5

... V A RXIDLE SS REFCLK_P REFCLK_N RX_P RX_N TX_P TX_N J VREFS Transparent top view. Fig 3. Ball mapping PX1011B_4 Product data sheet PX1011B-EL1/G PX1011B-EL1/N ball A1 PX1011BI-EL1/G index area Transparent top view RXDATA6 RXDATA4 RXDATA3 RXDATA7 RXDATA5 DDD2 SS DDD2 DDA2 DDA1 V TMS V DDD1 DDD1 TCK ...

Page 6

... NXP Semiconductors 7.2 Pin description The PHY input and output pins are described in output is defined from the perspective of the PHY. Thus a signal on a pin described as an output is driven by the PHY and a signal on a pin described as an input is received by the PHY. A basic description of each pin is provided. ...

Page 7

... NXP Semiconductors Table 9. Symbol RXVALID PHYSTATUS RXIDLE RXSTATUS0 RXSTATUS1 RXSTATUS2 Table 10. Symbol TXCLK RXCLK REFCLK_P REFCLK_N PVT VREFS Table 11. Symbol TMS TRST_N TCK TDI TDO PX1011B_4 Product data sheet PXPIPE interface status signals Pin Type Signaling C8 output SSTL_2 D8 output SSTL_2 A2 output ...

Page 8

... NXP Semiconductors Table 12. Symbol V DDA1 V DDA2 V DDD1 V DDD2 V DDD3 Functional description The main function of the PHY is to convert digital data into electrical signals and vice versa. The PCI Express PHY handles the low level PCI Express protocol and signaling. The PX1011B PCI Express PHY consists of the Physical Coding Sub-layer (PCS), a Serializer and De-serializer (SerDes) and a set of I/Os (pads) ...

Page 9

... NXP Semiconductors The de-serializer or Serial-to-Parallel converter (S2P) de-serializes this data into 10-bits parallel data. Since the S2P has no knowledge about the data, the word alignment is still random. This is fixed in the digital domain by the PCS block. It first detects a 10-bit comma character (K28.5) from the random data stream and aligns the bits. Then it converts the 10-bit raw data into 8-bit words using 8b/10b decoding ...

Page 10

... NXP Semiconductors RESET_N PHYSTATUS Fig 4. 8.5 Power management The power management signals allow the PHY to manage power consumption. The PHY meets all timing constraints provided in the PCI Express base specification regarding clock recovery and link training for the various power states. ...

Page 11

... NXP Semiconductors Table 13. Summary of power management state PWRDWN[1:0] Power management state 00b P0, normal operation 01b P0s, power saving state 10b P1, lower power state 11b illegal, PHY will enter P1 [1] TXIDLE = 0 [2] TXIDLE = 1 8.6 Receiver detect When the PHY is in the P1 state, it can be instructed to perform a receiver detection operation to determine if there is a receiver at the other end of the link ...

Page 12

... NXP Semiconductors • The PHY continues to provide the received data on the PXPIPE interface, behaving exactly like normal data reception. • The PHY transitions from normal transmission of data from the PXPIPE interface to looping back the received data at a symbol boundary. The PHY begins to loopback data when the MAC asserts RXDET_LOOPB while doing normal data transmission ...

Page 13

... NXP Semiconductors RXDATA[7:0] RXDET_LOOPB TX_P, TX_N Fig 7. 8.8 Electrical idle The PCI Express Base Specification requires that devices send an Electrical Idle ordered-set before TX goes to the electrical idle state. The timing diagram of TXCLK TXDATA[7:0] TXDATAK TXIDLE TX_P, TX_N Fig 8. PX1011B_4 Product data sheet ...

Page 14

... NXP Semiconductors Table 14 Table 14. PWRDWN[1:0] P0: 00b P0s: 01b P1: 10b 8.9 Clock tolerance compensation The PHY receiver contains an elastic buffer used to compensate for differences in frequencies between bit rates at the two ends of a link. The elastic buffer is capable of holding at least seven symbols to handle worst case differences (600 ppm) in frequency and worst case intervals between SKP ordered-sets. The PHY is responsible for inserting or removing SKP symbols in the received data stream to avoid elastic buffer overfl ...

Page 15

... NXP Semiconductors RXDATA[7:0] RXSTATUS2, RXSTATUS1, RXSTATUS0 Fig 10. Clock correction - remove a SKP 8.10 Error detection The PHY is responsible for detecting receive errors of several types. These errors are signaled to the MAC layer using the receiver status signals RXSTATUS. Table 15. Operating mode Received data OK ...

Page 16

... NXP Semiconductors 8.10.1 8b/10b decode errors For a detected 8b/10b decode error, the PHY places an EDB (EnD Bad) symbol in the data stream in place of the bad byte, and encodes RXSTATUS with a decode error during the clock cycle when the effected byte is transferred across the parallel interface. In Figure 11 an 8b/10b decode error ...

Page 17

... NXP Semiconductors RXDATA[7:0] RXSTATUS2, RXSTATUS1, RXSTATUS0 Fig 13. Elastic buffer underflow For an elastic buffer overflow, the overflow is signaled during the clock cycle where the dropped symbol would have appeared in the data stream. In the timing diagram of Figure 14, the PHY is receiving a repeating set of symbols Rx-a through Rx-z. The elastic buffer overfl ...

Page 18

... NXP Semiconductors 8.12 Setting negative disparity To set the running disparity to negative, the MAC asserts TXCOMP for one clock cycle that matches with the data that transmitted with negative disparity. TXDATA[7:0] TX_P, TX_N Fig 16. Setting negative disparity 8.13 JTAG boundary scan interface Joint Test Action Group (JTAG) or IEEE 1149 ...

Page 19

... NXP Semiconductors 9. Limiting values Table 16. In accordance with the Absolute Maximum Rating System (IEC 60134). Symbol V DDD1 V DDD2 V DDD3 DDA1 V DDA2 V esd T stg amb [1] Human Body Model: ANSI/EOS/ESD-S5.1-1994, standard for ESD sensitivity testing, Human Body Model - Component level; Electrostatic Discharge Association, Rome, NY, USA. ...

Page 20

... NXP Semiconductors 11. Characteristics Table 18. PCI Express PHY characteristics Symbol Parameter Supplies V digital supply voltage 1 DDD1 V digital supply voltage 2 DDD2 V digital supply voltage 3 DDD3 V supply voltage DD V analog supply voltage 1 DDA1 V analog supply voltage 2 DDA2 I digital supply current 1 DDD1 I digital supply current 2 ...

Page 21

... NXP Semiconductors Table 18. PCI Express PHY characteristics Symbol Parameter dV/dt rate of change of voltage V differential input HIGH voltage IH V differential input LOW voltage IL duty cycle on pin REFCLK REFCLK Transmitter UI unit interval V differential peak-to-peak output TX_DIFFp-p voltage t maximum time between the jitter TX_EYE_m-mJITTER ...

Page 22

... NXP Semiconductors REFCLK+ minus REFCLK Fig 17. Differential measurement points Table 19. PXPIPE characteristics Symbol Parameter f RXCLK frequency RXCLK f TXCLK frequency TXCLK V voltage on pin VREFS VREFS V SSTL_2 HIGH-level output voltage OH(SSTL2) V SSTL_2 LOW-level output voltage OL(SSTL2) V SSTL_2 HIGH-level input voltage IH(SSTL2) V SSTL_2 LOW-level input voltage IL(SSTL2) Input signals ...

Page 23

... NXP Semiconductors differential Fig 19. Transition eye Fig 20. Non transition eye PX1011B_4 Product data sheet 0.6 0.5 0.4 signal (V) 0.3 0.2 0.1 0 0.1 0.2 0.3 0.4 0.5 0.6 0.2 0.1 0 0.1 0 nominal V amb DD 0.6 0.5 differential 0.4 signal (V) 0.3 0.2 0.1 0 0.1 ...

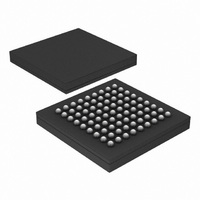

Page 24

... NXP Semiconductors 12. Package outline LFBGA81: plastic low profile fine-pitch ball grid array package; 81 balls; body 1.05 mm ball A1 index area ball A1 index area DIMENSIONS (mm are the original dimensions) A UNIT max. 0.4 1.20 0.5 mm 1.6 0.3 0.95 0.4 OUTLINE VERSION IEC SOT643-1 Fig 21. Package outline SOT643-1 (LFBGA81) ...

Page 25

... NXP Semiconductors 13. Soldering of SMD packages This text provides a very brief insight into a complex technology. A more in-depth account of soldering ICs can be found in Application Note AN10365 “Surface mount reflow soldering description” . 13.1 Introduction to soldering Soldering is one of the most common methods through which packages are attached to Printed Circuit Boards (PCBs), to form electrical circuits ...

Page 26

... NXP Semiconductors 13.4 Reflow soldering Key characteristics in reflow soldering are: • Lead-free versus SnPb soldering; note that a lead-free reflow process usually leads to higher minimum peak temperatures (see reducing the process window • Solder paste printing issues including smearing, release, and adjusting the process window for a mix of large and small components on one board • ...

Page 27

... Appendix 14.1 Errata added 2009-09-01 The PX1011B (types PX1011B-EL1/G, PX1011BI-EL1/G and PX1011B-EL1/N) is reported to sporadically produce communication failures in Intel DX58S0-based systems in which the PCIe transmitter has full Active Power State Management (ASPM) capability, and particularly when L0s mode is supported. ...

Page 28

... NXP Semiconductors 15. Abbreviations Table 22. Acronym BER BIST CMOS CRC EMI ESD FPGA LTSSM MAC P2S PCI PCS PHY PLL PIPE PVT S2P SerDes SKP SSTL_2 16. References [1] PCI Express Base Specification — Rev. 1.0a - PCISIG [2] PHY Interface for the PCI Express Architecture (PIPE) Specification Version 1.00 — ...

Page 29

... Right to make changes — NXP Semiconductors reserves the right to make changes to information published in this document, including without limitation specifications and product descriptions, at any time and without notice ...

Page 30

... NXP Semiconductors 20. Contents 1 General description . . . . . . . . . . . . . . . . . . . . . . 1 2 Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1 2.1 PCI Express interface . . . . . . . . . . . . . . . . . . . . 1 2.2 PHY/MAC interface 2.3 JTAG interface . . . . . . . . . . . . . . . . . . . . . . . . . 2 2.4 Power management . . . . . . . . . . . . . . . . . . . . . 2 2.5 Clock 2.6 Miscellaneous . . . . . . . . . . . . . . . . . . . . . . . . . . 2 3 Quick reference data . . . . . . . . . . . . . . . . . . . . . 2 4 Ordering information . . . . . . . . . . . . . . . . . . . . . 3 5 Marking . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3 6 Block diagram . . . . . . . . . . . . . . . . . . . . . . . . . . 4 7 Pinning information . . . . . . . . . . . . . . . . . . . . . . 5 7.1 Pinning . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5 7 ...