EPM9320RI208-20 Altera, EPM9320RI208-20 Datasheet

EPM9320RI208-20

Specifications of EPM9320RI208-20

Available stocks

Related parts for EPM9320RI208-20

EPM9320RI208-20 Summary of contents

Page 1

... PD1 t (ns) FSU t (ns) FCO f (MHz) CNT Altera Corporation DS-M9000-6.5 Includes MAX 9000A ® High-performance CMOS EEPROM-based programmable logic devices (PLDs) built on third-generation Multiple Array MatriX (MAX ® ) architecture 5.0-V in-system programmability (ISP) through built-in IEEE Std. 1149.1 Joint Test Action Group (JTAG) interface Built-in JTAG boundary-scan test (BST) circuitry compliant with IEEE Std ...

Page 2

... MAX 9000 device package types include plastic J-lead chip carrier (PLCC), power quad flat pack (RQFP), ceramic pin-grid array (PGA), and ball-grid array (BGA) packages. Perform a complete thermal analysis before committing a design to this device package. See Application Note 74 (Evaluating Power for Altera TM TM parallel port download Note (1) ...

Page 3

... Altera Corporation MAX 9000 Programmable Logic Device Family Data Sheet The MAX 9000 family of in-system-programmable, high-density, high- performance EPLDs is based on Altera’s third-generation MAX architecture. Fabricated on an advanced CMOS technology, the EEPROM- based MAX 9000 family provides 6,000 to 12,000 usable gates, pin-to-pin delays as fast as 10 ns, and counter speeds 144 MHz ...

Page 4

... MAX 9000 devices offer the MultiVolt feature, which allows output drivers to be set for either 3.3-V or 5.0-V operation in mixed- voltage systems. 4 Altera Corporation ...

Page 5

... Description Altera Corporation MAX 9000 Programmable Logic Device Family Data Sheet The MAX 9000 family is supported by Altera’s MAX+PLUS II development system, a single, integrated software package that offers schematic, text—including VHDL, Verilog HDL, and the Altera Hardware Description Language (AHDL)—and waveform design entry, compilation and logic synthesis, simulation and timing analysis, and device programming ...

Page 6

... LAB. Each LAB is also fed by two low-skew global clocks and one global clear that can be used for register control signals in all 16 macrocells. 6 IOC IOC IOC IOC IOC IOC 7. Multiple LABs are linked together via the FastTrack IOC IOC IOC FastTrack Interconnect IOC IOC IOC Altera Corporation ...

Page 7

... Figure 2. MAX 9000 Logic Array Block DIN1 DIN2 DIN3 DIN4 Row FastTrack Interconnect LAB Local Array (114 Channels) Shared Expander Signals Altera Corporation MAX 9000 Programmable Logic Device Family Data Sheet Global Control Select GCLK1 GCLK2 GCLR GOE 33 Macrocell 1 Macrocell 2 Macrocell 3 ...

Page 8

... Parallel expanders, which are product terms borrowed from adjacent macrocells Figure 3. Global Global Clear Clocks 2 Macrocell Programmable Register Input Select Register Bypass PRN D/T Q Clock/ Enable ENA Select CLRN VCC Clear Select Altera Corporation To Row or Column FastTrack Interconnect Local Array Feedback ...

Page 9

... Altera Corporation MAX 9000 Programmable Logic Device Family Data Sheet For registered functions, each macrocell register can be individually programmed for operation with programmable clock control. The flipflop can also be bypassed for combinatorial operation. During design entry, the user specifies the desired register type; the MAX+PLUS II software then selects the most efficient register operation for each registered function to optimize resource utilization ...

Page 10

... Figure 4. MAX 9000 Shareable Expanders Shareable expanders can be shared by any or all macrocells in the LAB. 33 Row FastTrack Interconnect Signals 10 LAB Local Array 16 Local 16 Shared Feedbacks Expanders + incurred LOCAL SEXP Figure 4 shows how shareable Macrocell Product-Term Logic Product-Term Select Matrix Macrocell Product-Term Logic Altera Corporation ...

Page 11

... Interconnect Array Signals 16 Local Feedbacks Altera Corporation MAX 9000 Programmable Logic Device Family Data Sheet Parallel Expanders Parallel expanders are unused product terms that can be allocated to a neighboring macrocell to implement fast, complex logic functions. Parallel expanders allow product terms to directly feed the macrocell OR logic, with five product terms provided by the macrocell and 15 parallel expanders provided by neighboring macrocells in the LAB ...

Page 12

... FPGAs requires switch matrices to connect a variable number of routing paths, increasing the delays between logic resources and reducing performance. with row and column interconnects For example macrocell requires 14 product terms, the PEXP . PEXP Figure 6 shows the interconnection of four adjacent LABs Altera Corporation ...

Page 13

... Each LAB is named on the basis of its physical row ( etc.) and column ( etc.) position within the device. Column FastTrack Interconnect IOC1 IOC8 See Figure 7 for details. IOC1 IOC8 Altera Corporation MAX 9000 Programmable Logic Device Family Data Sheet IOC1 IOC10 Row FastTrack Interconnect LAB A1 LAB B1 ...

Page 14

... The MAX+PLUS II Compiler optimizes connections to a column channel automatically. 14 Figure 7 shows how a macrocell drives the row and To LAB Local Array Additional multiplexer provides column-to-row path if macrocell drives row channel. 48 Column Channels Each macrocell drives one of three column channels. Altera Corporation ...

Page 15

... Altera Corporation MAX 9000 Programmable Logic Device Family Data Sheet A row interconnect channel can be fed by the output of the macrocell through a 4-to-1 multiplexer that the macrocell shares with three column channels. If the multiplexer is used for a macrocell-to-row connection, the three column signals can access another row channel via an additional 3-to-1 multiplexer ...

Page 16

... IOC1 Each IOC is driven by a 17-to-1 multiplexer. 17 Figure 2 on page shows the IOC block diagram. Signals enter the MAX 9000 IOC10 Column FastTrack Interconnect 7). Altera Corporation Each IOC can drive up to two column channels. ...

Page 17

... Altera Corporation MAX 9000 Programmable Logic Device Family Data Sheet Figure 10. MAX 9000 IOC Peripheral Control Bus [12..0] OE [7.. Row or Column FastTrack Interconnect 13 From Row or Column FastTrack Interconnect CLK [3..0] 4 ENA [5..0] 6 VCC CLR [1..0] 2 I/O pins can be used as input, output, or bidirectional pins. Each IOC has an IOC register with a clock enable input ...

Page 18

... Row F Row E Row E Row B Row B Row A Row A Row D Row D Row C Row C Row B/GOE Row B/GOE GCLK1 GCLK1 GCLK2 GCLK2 Row D Row D Row C Row C Altera Corporation EPM9560 EPM9560A Row G Row F Row E Row B Row A Row D Row C Row B/GOE GCLK1 GCLK2 Row D Row C pins CC ...

Page 19

... Because some in-circuit testers platforms have difficulties supporting an adaptive algorithm, Altera offers devices tested with a constant algorithm. Devices tested to the constant algorithm have an “F” suffix in the ordering code. ...

Page 20

... EEPROM cells. This process is repeated for each EEPROM address. Verify. Verifying an Altera device in-system involves shifting in addresses, applying the read pulse to verify the EEPROM cells, and shifting out the data for comparison. This process is repeated for each EEPROM address ...

Page 21

... Altera Corporation MAX 9000 Programmable Logic Device Family Data Sheet By combining the pulse and shift times for each of the programming stages, the program or verify time can be derived as a function of the TCK frequency, the number of devices, and specific target device(s). Because different ISP-capable devices have a different number of EEPROM cells, both the total fixed and total variable times are unique for a single device ...

Page 22

... Cycle VTCK 1,806,000 2,090,000 2,374,000 2,658,000 Units 50 kHz 71.11 s 79.30 s 87.49 s 95.70 s Units 50 kHz 36.27 s 41.95 s 47.63 s 53.31 s Altera Corporation ...

Page 23

... MAX 9000 Programmable Logic Device Family Data Sheet MAX 9000 devices can be programmed on Windows-based PCs with an Altera Logic Programmer card, the Master Programming Unit (MPU), and the appropriate device adapter. The MPU performs continuity checking to ensure adequate electrical contact between the adapter and the device ...

Page 24

... Although the EPM9320A and EPM9560A devices support the IDCODE instruction, the EPM9320 and EPM9560 devices do not. shows the timing requirements for the JTAG signals. Boundary-Scan Register Length 504 552 600 648 Note (1) IDCODE (32 Bits) Part Number Manufacturer’s (16 Bits) (2) Identity (11 Bits) 00001101110 00001101110 00001101110 00001101110 Altera Corporation Tables Bit ...

Page 25

... Figure 11. MAX 9000 JTAG Waveforms Table 13 devices. f For detailed information on JTAG operation in MAX 9000 devices, refer to Application Note 39 (IEEE 1149.1 (JTAG) Boundary-Scan Testing in Altera Devices). Altera Corporation MAX 9000 Programmable Logic Device Family Data Sheet TMS TDI t JCP t t JCH JCL ...

Page 26

... Numbers without parentheses are for 5.0-V devices or outputs. ™ option turned on for the LAB local array LPA Figure 12. Test patterns can be used and then 464 (703 ) Device Output 250 (8. Device input rise and fall times < VCC To Test System C1 (includes JIG capacitance) Altera Corporation ...

Page 27

... Junction temperature J t Input rise time R t Input fall time F Altera Corporation MAX 9000 Programmable Logic Device Family Data Sheet Tables 14 through 20 provide information on absolute maximum ratings, recommended operating conditions, operating conditions, and capacitance for MAX 9000 devices. With respect to ground ...

Page 28

... EPM9320 EPM9400 EPM9480 EPM9560 Unit V = ground, 106 I no load (11) (6) Min Max 2.0 V CCINT –0.5 (8) 2.4 (8) 2.4 = 3.00 V (8) V – CCIO 0.2 (8) 0.45 (8) 0.45 (8) –10 –40 Min Max Note (10) Min Max 132 140 146 Altera Corporation Unit + V 0 Note (10) Unit Unit ...

Page 29

... Notes to tables: (1) See the Operating Requirements for Altera Devices Data (2) Minimum DC input on I/O pins is –0.5 V and on the four dedicated input pins is –0.3 V. During transitions, the inputs may undershoot to –2 overshoot to 7.0 V for periods shorter than 20 ns under no-load conditions. ...

Page 30

... MAX 9000 timing model and these timing parameters can be used to estimate MAX 9000 device performance. For more information on calculating MAX 9000 timing delays, see Application Note 77 (Understanding MAX 9000 Figure 14 shows the delays that Figure 14 is expressed as a worst-case Timing). Altera Corporation ...

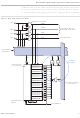

Page 31

... Figure 14. MAX 9000 Timing Model Altera Corporation MAX 9000 Programmable Logic Device Family Data Sheet 31 ...

Page 32

... 1.0 (3) (4) (4) 144.9 Speed Grade -15 -20 Max Min Max Min 10.0 15.0 10.8 16.0 16.2 16.4 11.4 16.6 5.0 6.0 0.0 0.0 4.8 1.0 (3) 7.0 1.0 (3) 6.9 8.5 117.6 100.0 Altera Corporation Unit Max 20 23.0 ns 23 8.5 ns 10.0 ns MHz ...

Page 33

... Register hold time H t Register preset time PRE t Register clear time CLR t FastTrack drive delay FTD t Low-power adder LPA Altera Corporation MAX 9000 Programmable Logic Device Family Data Sheet Note (1) Conditions -10 Min 2.4 2.0 (5) Speed Grade -15 -20 Max Min Max Min 3 ...

Page 34

... Altera Corporation Unit Max 1.5 ns 1.5 ns 2.0 ns 1 3.0 ns 0.5 ns 5.5 ns 2.5 ns 2 ...

Page 35

... Consumption The P and switching frequency, can be calculated using the guidelines given in Application Note 74 (Evaluating Power for Altera depends on the switching frequency and the application logic. The I I Altera Corporation MAX 9000 Programmable Logic Device Family Data Sheet ...

Page 36

... Figure 15 shows typical supply current versus frequency for MAX 9000 devices. Table 25 Constant B 0.33 0.31 0.33 0.29 0.26 0.31 estimate based on typical conditions with CC values should be verified CC Altera Corporation Constant C 0.056 0.024 0.053 0.064 0.052 0.024 ...

Page 37

... Frequency (MHz) EPM9400 1000 800 600 Typical I Active CC (mA) 400 42 MHz 200 Non-Turbo Frequency (MHz) Altera Corporation MAX 9000 Programmable Logic Device Family Data Sheet EPM9320A Typical I Active CC 118 MHz (mA) Turbo 75 100 125 EPM9480 Typical 118 MHz I Active CC (mA) Turbo ...

Page 38

... RQFP 280-Pin PGA 182 V10 183 U10 153 V17 C11 108 A18 1000 800 600 400 59 MHz 200 Non-Turbo Frequency (MHz) Note (1) (3) 356-Pin BGA AD13 AF14 AD1 AC24 A18 E23 A13 D3 Altera Corporation 144 MHz Turbo 100 125 ...

Page 39

... No Connect 29 (N.C.) (4) 56 VPP Total User 60 I/O Pins (5) Altera Corporation MAX 9000 Programmable Logic Device Family Data Sheet 208-Pin RQFP 280-Pin PGA 14, 20, 24, 31, 35, D4, D5, D16, E4, E5, E6, 41, 42, 43, 44, 46, E15, E16, F5, F15, G5, 47, 66, 85, 102, G15, H5, H15, J5, J15, K5, 110, 113, 114, 115, ...

Page 40

... Notes: (1) All pins not listed are user I/O pins. (2) Perform a complete thermal analysis before committing a design to this device package. See (Evaluating Power for Altera Devices) (3) During in-system programming, each device’s normal device operation, the unconnected. (4) The user I/O pin count includes dedicated input pins and all I/O pins. ...

Page 41

... Altera Corporation MAX 9000 Programmable Logic Device Family Data Sheet Table 28. EPM9480 Dedicated Pin-Outs Pin Name DIN1 (GCLK1) 182 DIN2 (GCLK2) 183 DIN3 (GCLR) 153 DIN4 (GOE TCK 49 TMS 79 TDI 108 TDO 14, 20, 24, 31, 35, 41, 42, GND 43, 44, 46, 47, 66, 85, 102, 110, 113, 114, 115, ...

Page 42

... AF20 12, 32, 52, 72, D26, F1, H1, K26, 157, 177, 197, N26, P1, U1, 217 W26, AE26, AF25, AF26 3, 23, 43, 63, 91, A1, A2, A21, B1, 108, 127, 156, B10, B24, D1, 176, 196, 216, H26, K1, M25, 243, 260, 279 R1, V26, AA1, AC25, AF5, AF8, AF19 Altera Corporation ...

Page 43

... EPM9560A devices are not offered in this package. (3) During in-system programming, each device’s normal device operation, the unconnected. (4) The user I/O pin count includes dedicated input pins and all I/O pins. Altera Corporation MAX 9000 Programmable Logic Device Family Data Sheet 240-Pin RQFP 280-Pin PGA – B6 ...

Page 44

... Copyright © 2003 Altera Corporation. All rights reserved. Altera, The Programmable Solutions Company, the 101 Innovation Drive stylized Altera logo, specific device designations, and all other words and logos that are identified as San Jose, CA 95134 trademarks and/or service marks are, unless noted otherwise, the trademarks and service marks of Altera (408) 544-7000 Corporation in the U ...

Page 45

... Altera Corporation MAX 9000 Programmable Logic Device Family Data Sheet 45 ...

Page 46

... MAX 9000 Programmable Logic Device Family Data Sheet 46 Altera Corporation ...